# PROGRAMMED DATA PROCESSOR-5 MAINTENANCE MANUAL

COPY NO.

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

Copyright 1964 by Digital Equipment Corporation

#### PREFACE

This manual contains information for the planning and execution of all tasks involved in the installation, operation, and maintenance of the Programmed Data Processor-5, a core memory, stored program, parallel, digital computer designed and manufactured by the Digital Equipment Corporation. Information in this manual is prepared for engineers and technicians familiar with digital logic techniques and digital computer principles, and is not intended to teach basic theory. The manual does attempt to describe and explain the operation of the PDP-5 computer in detail. Every attempt has been made to organize this manual to allow rapid access of information required for a specific task. In an attempt to emphasize the importance of study and planning before the actual performance of a physical task, the first portion of this manual contains expository information, and the last portion contains task-oriented information and detailed procedures.

This manual is organized into the following sections:

Section 1, Introduction and Description - Information of a general nature which is applicable to the entire PDP-5 system is contained in this chapter. The chapter contains a detailed summary which describes the system as consisting of a processor, core memory, and input/output facilities. An understanding of this information is a prerequisite for reading the chapters containing detailed theory.

Section 2, Processor; Section 3, Core Memory; and Section 4, Input/Output – These chapters contain detailed theory of operation for the three major logic elements which constitute the PDP-5. The function of each circuit is explained and the generation of all control signals is described in detail with the aid of references to the block schematic engineering drawings.

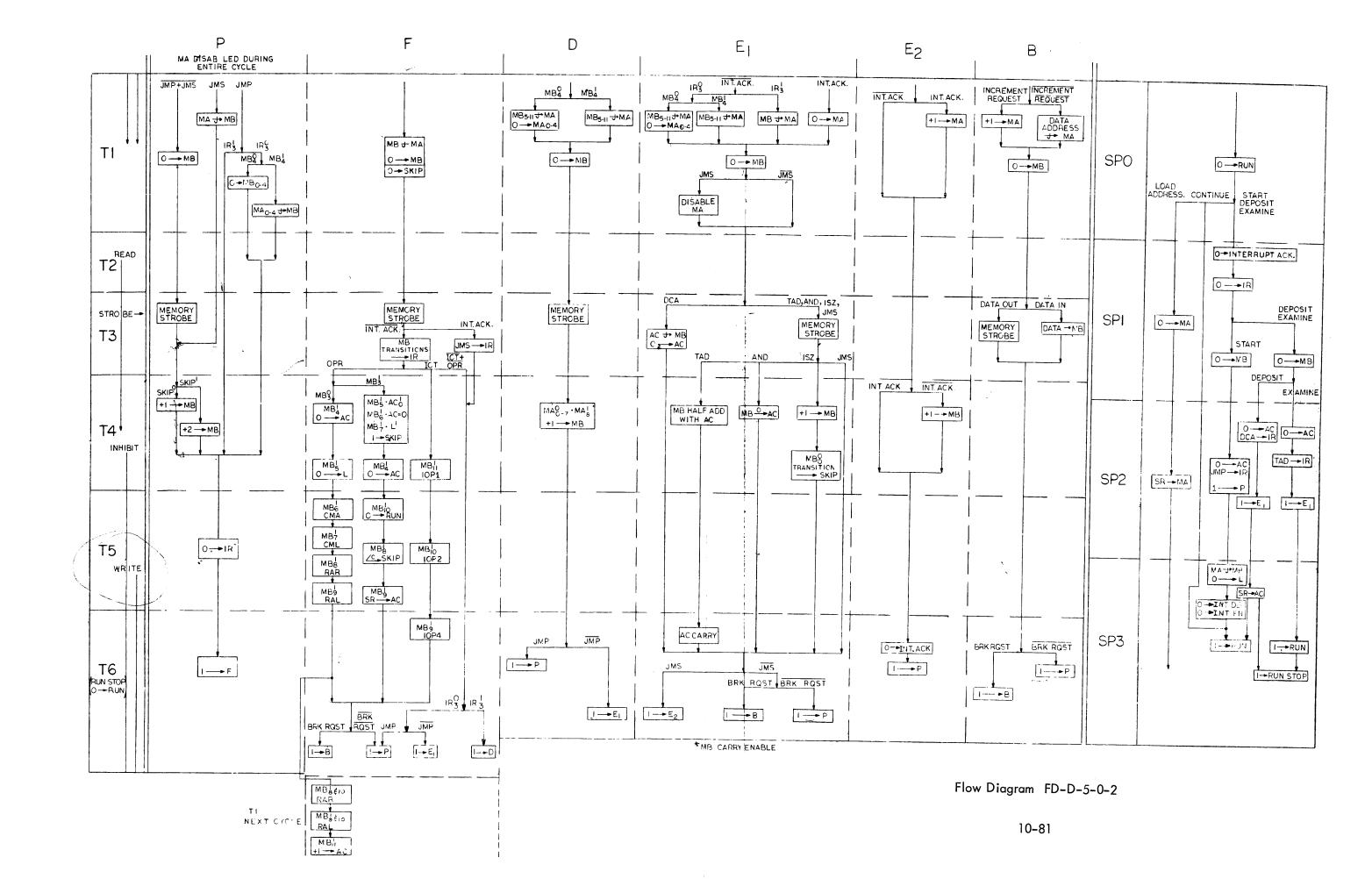

Section 5, Logic Function - All operations involved in the performance of computing functions are described in detail in this chapter with the aid of the engineering flow diagram. Operations are described in detail with regard to accomplishing a specific task and are not encumbered by explanations of circuit operations as described in the previous chapters. This chapter tends to integrate the reader's understanding of the functions performed by the processor, core memory, and input/output logic elements.

Section 6, Interface – The technical characteristics of the interface circuits of the PDP-5 are defined and described in detail in this chapter to allow adequate design and installation planning of special peripheral equipment.

Section 7, Installation - Information is contained in this chapter to allow personnel to plan and implement the installation of a PDP-5 system.

Section 8, Operation - The function of controls and indicators of the computer and the standard Teletype unit are listed, and procedures are given to allow operation of this system. These procedures are written to allow interpretation and expansion required for the performance of specific tasks.

Section 9, Maintenance – Planning information and specific detailed procedures are contained in this chapter to allow personnel to perform thorough preventive maintenance and rapid logical corrective maintenance of the standard PDP-5.

Section 10, Pertinent Documents - Reference material in the form of a list of publications and copies of the engineering drawings are reproduced in this chapter as an aid to understanding the information contained in the manual.

## CONTENTS

| Section |                                        | Page |

|---------|----------------------------------------|------|

| 1       | INTRODUCTION AND DESCRIPTION           | 1-1  |

|         | Computer Organization                  | 1-1  |

|         | Processor                              | 1-1  |

|         | Core Memory                            | 1-4  |

|         | Input/Output                           | 1-5  |

|         | Functional Description                 | 1-6  |

|         | Instructions                           | 1-6  |

|         | Major States                           | 1-9  |

|         | Time States                            | 1-10 |

|         | Physical Description                   | 1-11 |

|         | Specifications                         | 1-12 |

|         | Physical                               | 1-12 |

|         | Electrical                             | 1-13 |

|         | Ambient Conditions                     | 1-13 |

|         | Functional                             | 1-13 |

|         | Symbols and Terminology                | 1-14 |

| 2       | PROCESSOR                              | 2-1  |

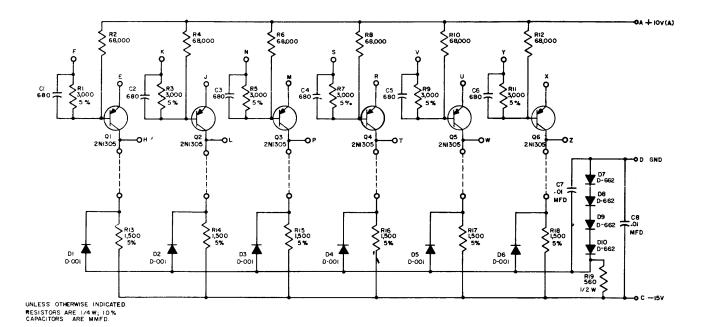

|         | Power Clear Generator (5)              | 2-1  |

|         | Special Pulse Generator (5)            | 2-2  |

|         | Timing Signal Generator (17)           | 2-3  |

|         | Operator Console (WD-D-5-0-10)         | 2-6  |

|         | Interlock and POWER Switches           | 2-6  |

|         | Key Circuits                           | 2-7  |

|         | Indicator Circuits                     | 2-7  |

|         | SWITCH REGISTER Toggle Switch Circuits | 2-7  |

|         | Run and IO Halt Control (5)            | 2-8  |

|         | Program Counter                        | 2-9  |

|         | Instruction Register (6)               | 2-9  |

|         | Major State Generator (6)              | 2-11 |

| Section |                                                | Page         |

|---------|------------------------------------------------|--------------|

|         | Memory Address Register Control (7)            | 2-14         |

|         | Memory Buffer Register Control (7)             | 2-17         |

|         | Accumulator Control (8)                        | 2-20         |

|         | Memory Address Register (9)                    | 2-23         |

|         | Memory Buffer Register (9)                     | 2-24         |

|         | Accumulator (9)                                | 2-25         |

|         | Link (9)                                       | 2-27         |

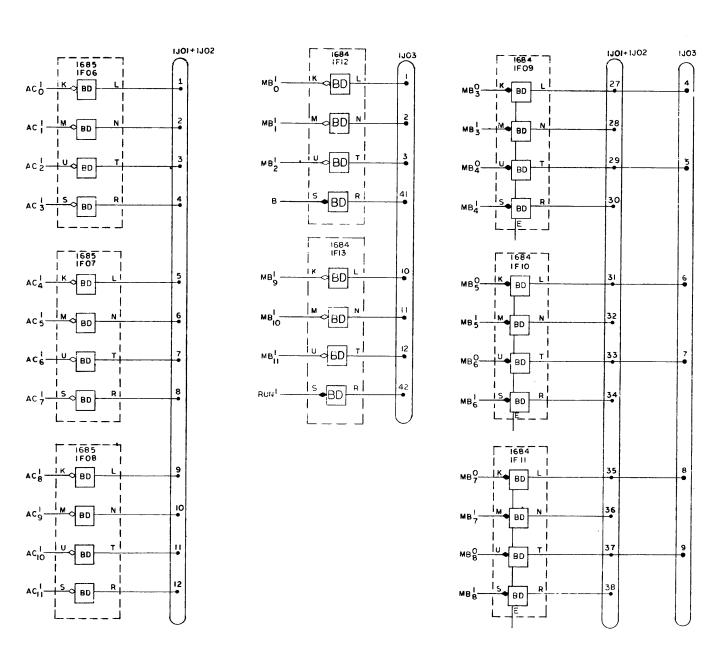

|         | Output Bus Drivers (31)                        | 2-27         |

|         | Input Mixer (14)                               | 2-28         |

| -       | Skip Control (8)                               | 2-28         |

|         | IOP Pulse Generator (6)                        | 2-31         |

|         | Program Interrupt Synchronization (8)          | 2-32         |

|         | Type 153 Automatic Multiply and Divide Option  | 2-33         |

| 3       | CORE MEMORY                                    | 3-1          |

|         | Memory Organization                            | 3-1          |

|         | Current Source                                 | 3-5          |

|         | Memory Drivers (17)                            | 3-7          |

|         | Address Selection (16)                         | 3-9          |

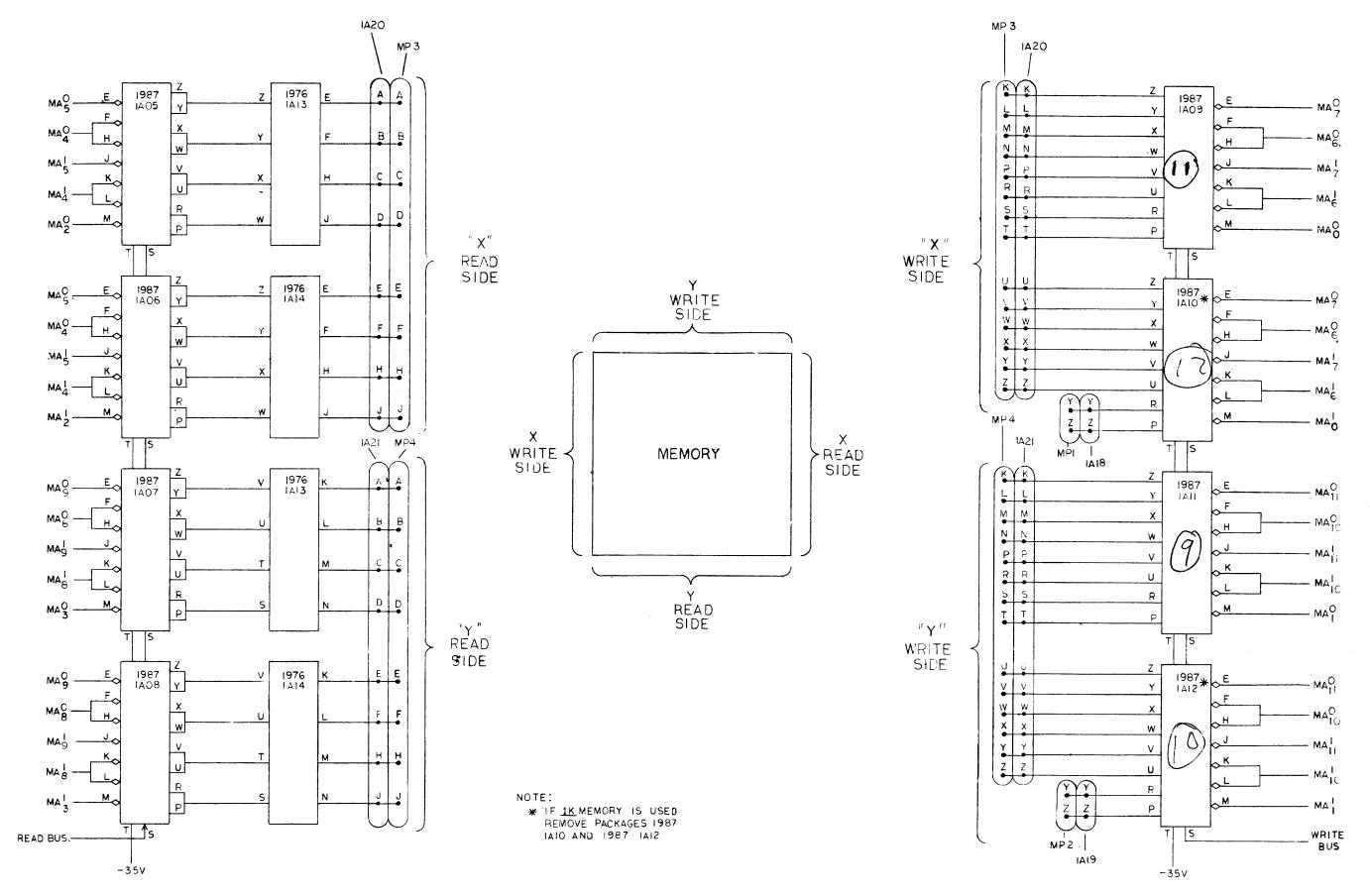

|         | Memory Diode Units and Core Array (11, 12)     | 3-10         |

|         | Inhibit Selections (17)                        | 3-11         |

|         | Sense Amplifiers (17)                          | 3-12         |

|         | Type 154 Memory Extension Control Option       | 3-13         |

|         | Type 155 Memory Module Option                  | 3-1 <i>7</i> |

| 4       | INPUT/OUTPUT                                   | 4-1          |

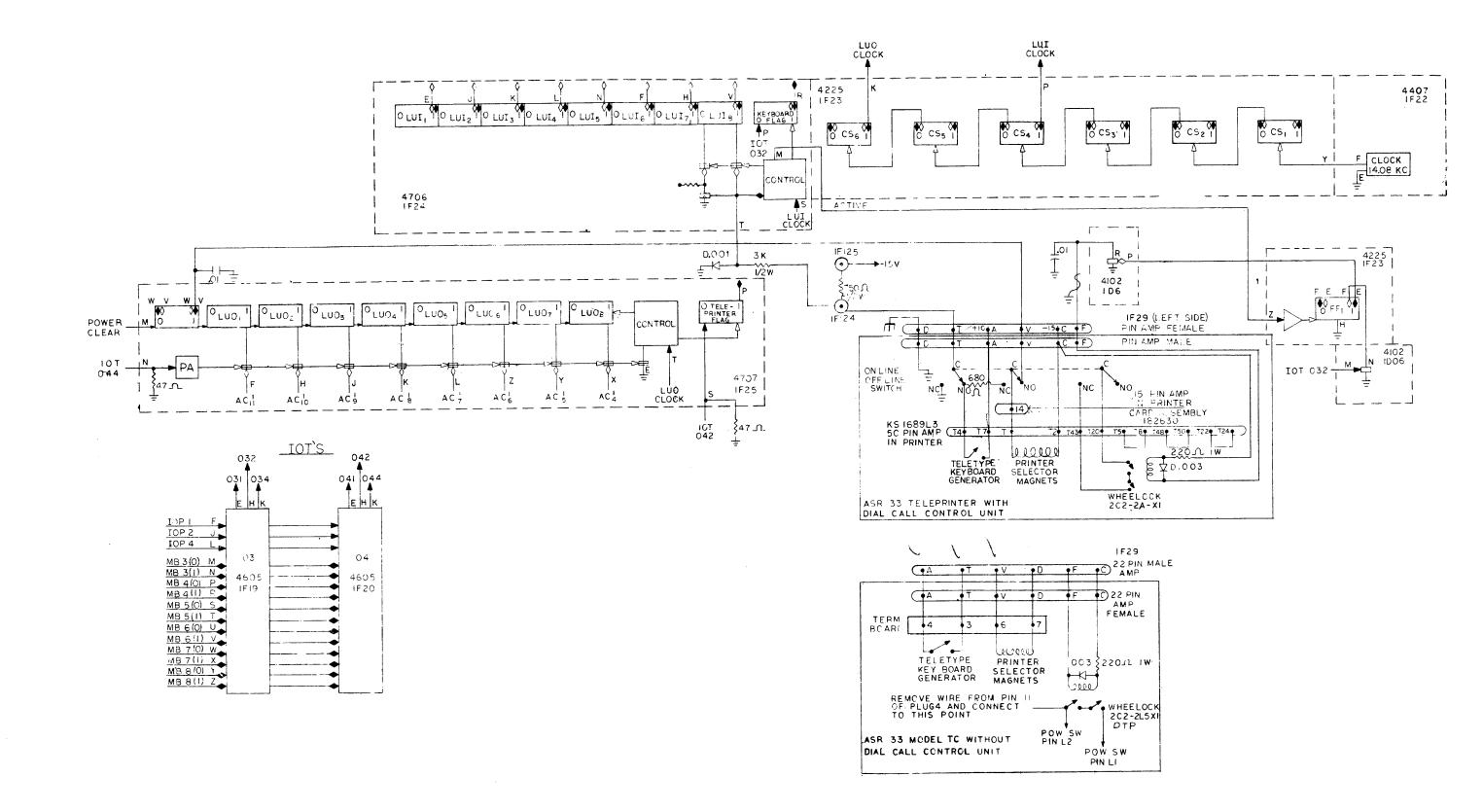

|         | Teletype Model 33 Automatic Send Receive Set   | 4-2          |

|         | Teletype Control (18)                          | 4-3          |

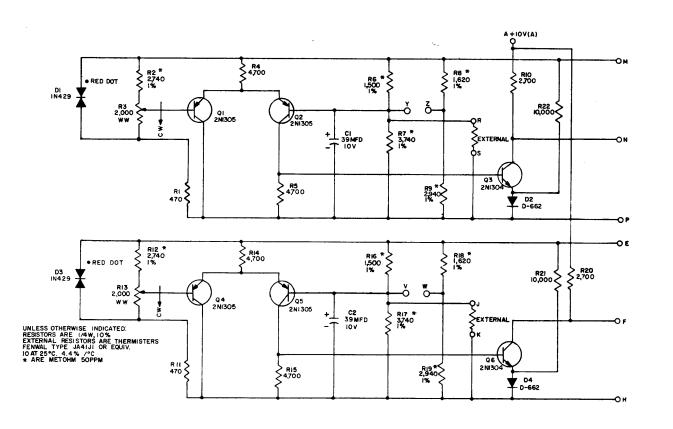

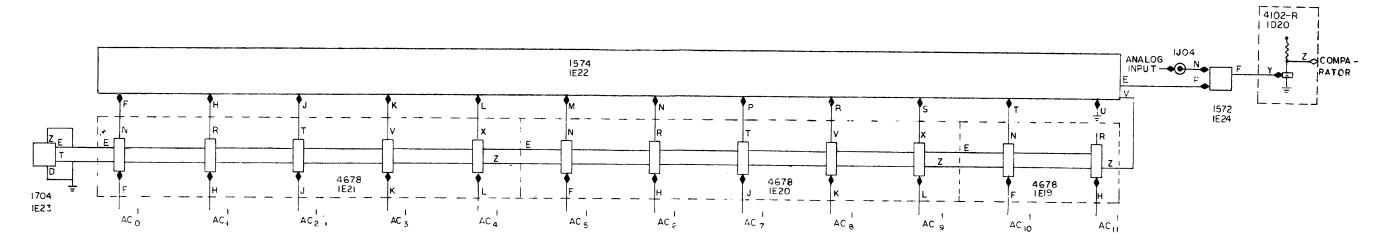

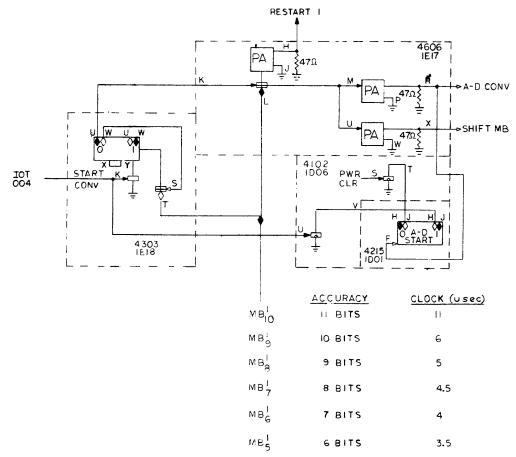

|         | Type 137 Analog-to-Digital Converter (137–2–1) | 4-6          |

| Section |                                                              | Page         |

|---------|--------------------------------------------------------------|--------------|

| 5       | LOGIC FUNCTION                                               | 5-1          |

|         | Manual Operation                                             | 5-1          |

|         | LOAD ADDRESS Key                                             | 5-2          |

|         | DEPOSIT Key                                                  | 5-2          |

|         | EXAMINE Key                                                  | 5-3          |

|         | START Key                                                    | 5-3          |

|         | CONTINUE Key                                                 | 5-4          |

|         | STOP Key                                                     | 5-4          |

|         | SINGLE STEP and SINGLE INST. Keys                            | 5-5          |

|         | Automatic Operation                                          | 5-5          |

|         | Instructions                                                 | 5-5          |

|         | Logical AND (AND)                                            | 5-5          |

|         | Twos Complement Add (TAD)                                    | 5 <b>-</b> 7 |

|         | Index and Skip if Zero (ISZ)                                 | 5-8          |

|         | Deposit and Clear Accumulator (DCA)                          | 5 <b>-</b> 8 |

|         | Jump to Subroutine (JMS)                                     | 5-9          |

|         | Jump (JMP)                                                   | 5-10         |

|         | Input/Output Transfer (IOT)                                  | 5-11         |

|         | Operate (OPR)                                                | 5-12         |

|         | Program Interrupt                                            | 5-13         |

|         | Data Break                                                   | 5-15         |

| 6       | INTERFACE                                                    | 6-1          |

|         | Loading and Driving Definitions                              | 6-8          |

|         | Base Load                                                    | 6-8          |

|         | Pulse Load                                                   | 6-8          |

|         | Pulsed Emitter Load                                          | 6-9          |

|         | DC Emitter Load                                              | 6-9          |

|         | Power Clear Generator (5)                                    | 6-10         |

|         | Special Pulse Generator (5) and Timing Signal Generator (17) | 6-10         |

| Section |                                       | Page        |

|---------|---------------------------------------|-------------|

|         | Run and I/O Halt Control (5)          | 6-10        |

|         | Run                                   | 6-10        |

|         | I/O Halt and Restart                  | 6-11        |

|         | Major State Generator (6)             | 6-12        |

|         | Break Request                         | 6-12        |

|         | Break                                 | 6-12        |

|         | Memory Address Register Control (7)   | 6-12        |

|         | Address Accepted                      | 6-12        |

|         | Increment Request                     | 6-13        |

|         | Memory Buffer Register Control (7)    | 6-13        |

|         | Transfer Direction                    | 6-13        |

|         | Data                                  | 6-14        |

|         | Accumulator Control (8)               | 6-14        |

|         | Clear AC                              | 6-14        |

|         | Address Accepted                      | 6-14        |

|         | Memory Address Register (9)           | 6-15        |

|         | Memory Buffer Register (9)            | 6-15        |

|         | MB Outputs                            | 6-15        |

|         | Data Bit Inputs                       | 6-16        |

|         | Increment MB                          | 6-16        |

|         | Accumulator (9) and Input Mixer (14)  | 6-17        |

|         | AC Outputs                            | 6-17        |

|         | AC Inputs                             | 6-17        |

|         | Skip Control (8)                      | 6-18        |

|         | IOP Pulse Generator (6)               | 6-18        |

|         | Program Interrupt Synchronization (6) | 6-19        |

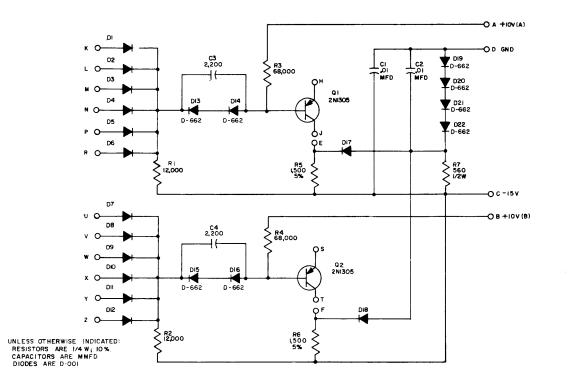

|         | Device Selector (RS-4605)             | 6-19        |

| 7       | INSTALLATION                          | <i>7</i> -1 |

|         | Site Preparation                      | 7-1         |

| Section |                                                  | Page |

|---------|--------------------------------------------------|------|

|         | Preparation for Shipment                         | 7-3  |

|         | Installation Procedure                           | 7-5  |

| 8       | OPERATION                                        | 8-1  |

|         | Controls and Indicators                          | 8-1  |

|         | Operating Procedures                             | 8-8  |

|         | Manual Data Storage and Modification             | 8-8  |

|         | Loading Data Under Program Control               | 8-10 |

|         | Off-Line Teletype Operation                      | 8-11 |

|         | Assembling Programs with PAL                     | 8-13 |

|         | Teletype Code                                    | 8-14 |

|         | Programming                                      | 8-19 |

| 9       | MAINTENANCE                                      | 9-1  |

|         | Preventive Maintenance                           | 9-4  |

|         | Mechanical Checks                                | 9-4  |

|         | Power Supply Checks                              | 9-5  |

|         | Marginal Checks                                  | 9-6  |

|         | Memory Current Check                             | 9-11 |

|         | Sense Amplifier Check                            | 9-12 |

|         | Type 137 Analog-to-Digital Converter Maintenance | 9-12 |

|         | Converter Check                                  | 9-13 |

|         | Integrating Single Shot Check and Adjustment     | 9-16 |

|         | Precision Power Supply Check and Adjustment      | 9-16 |

|         | Digital-to-Analog Converter Check and Adjustment | 9-17 |

|         | The Difference Amplifier Check and Adjustment    | 9-22 |

|         | Corrective Maintenance                           | 9-23 |

|         | Preliminary Investigation                        | 9-24 |

|         | System Troubleshooting                           | 9-25 |

|         | Memory Troubleshooting                           | 9-25 |

|         | Logic Troubleshooting                            | 9-27 |

| Section |             |                                                                           | Page |

|---------|-------------|---------------------------------------------------------------------------|------|

|         |             | Signal Tracing                                                            | 9-28 |

|         |             | Aggravation Tests                                                         | 9-28 |

|         | Cir         | cuit Troubleshooting                                                      | 9-29 |

|         |             | Module Circuits                                                           | 9-29 |

|         |             | In-Line Dynamic Tests                                                     | 9-30 |

|         |             | In-Line Marginal Checks                                                   | 9-3  |

|         |             | Static Bench Tests                                                        | 9-32 |

|         |             | Dynamic Bench Tests                                                       | 9-34 |

|         | Rep         | pair                                                                      | 9-34 |

|         | Spc         | re Parts                                                                  | 9-3  |

|         |             | Standard PDP-5 Spare Module List                                          | 9-3  |

|         |             | Type 34B Oscilloscope Display Spare Module List                           | 9-38 |

|         |             | Type 50 Magnetic Tape Transport Spare  Module List                        | 9-3  |

|         |             | Type 57A Automatic Tape Control with Type 157 Interface Spare Module List | 9-38 |

|         |             | Type 75A High Speed Perforated Tape Punch and Control Spare Module List   | 9-3  |

|         |             | Type 137 Analog-to-Digital Converter Spare Module List                    | 9-3  |

|         |             | Type 139 General Purpose Multiplexer and Control Spare Module List        | 9-38 |

|         |             | Type 153 Automatic Multiply and Divide Spare Module List                  | 9-3  |

|         |             | Type 154 Memory Extension Control Spare Module List                       | 9-3  |

|         | turk turk e | Type 155 Memory Module Spare Module List                                  | 9-3  |

|         |             | Type 350 Incremental Plotter and Control Spare Module List                | 9-3  |

|         |             | Type 552 DECtape (formerly called Microtape) Control Spare Module List    | 9-3  |

|         |             | Type 750 High Speed Tape Reader and Control Spare Module List             | 9-39 |

|         | Va          | lidation Test                                                             | 9-39 |

| Section |                                                      | Page |

|---------|------------------------------------------------------|------|

|         | Log Entry                                            | 9-40 |

| 10      | PERTINENT DOCUMENTS                                  | 10-1 |

|         | Publications                                         | 10-1 |

|         | Drawings                                             | 10-2 |

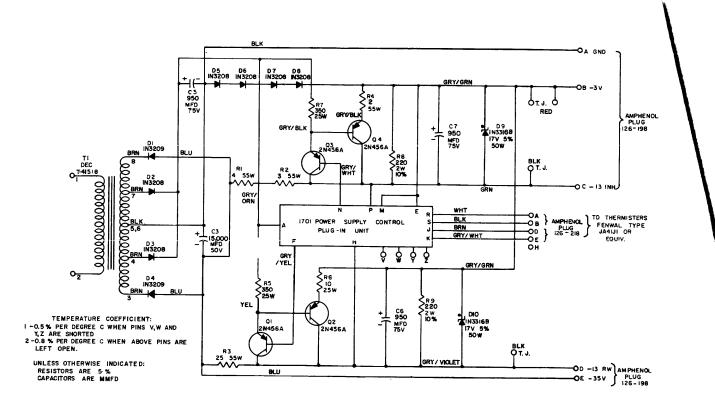

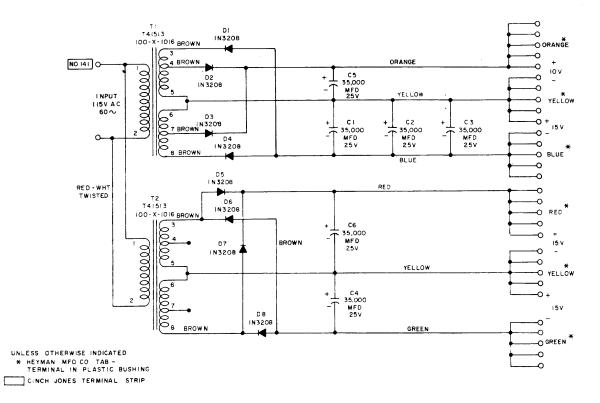

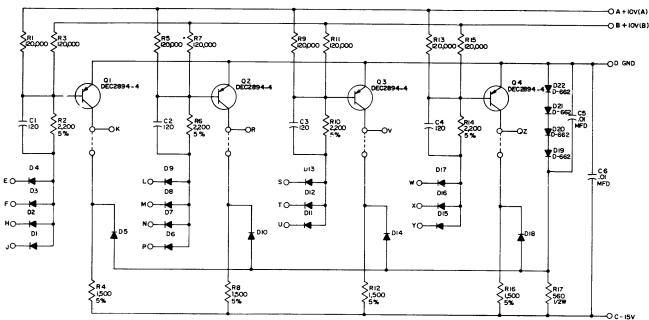

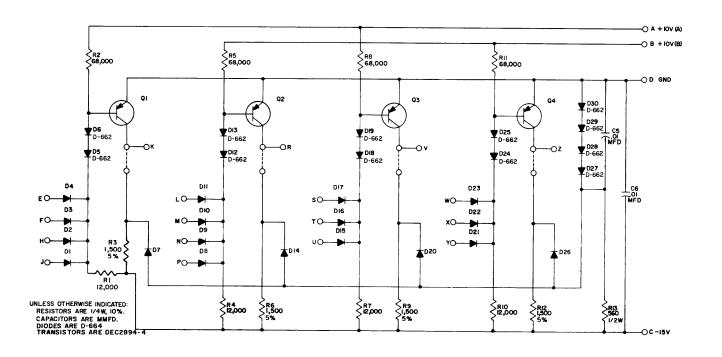

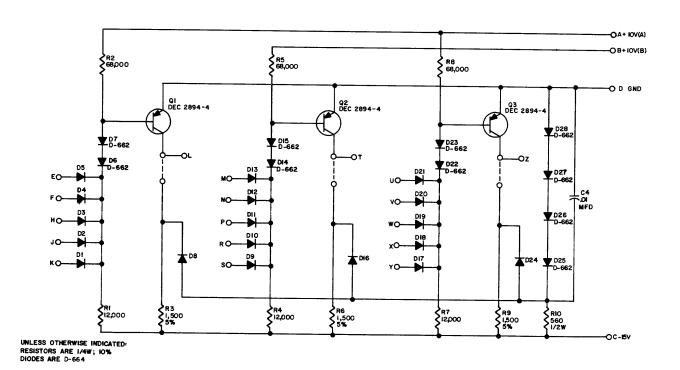

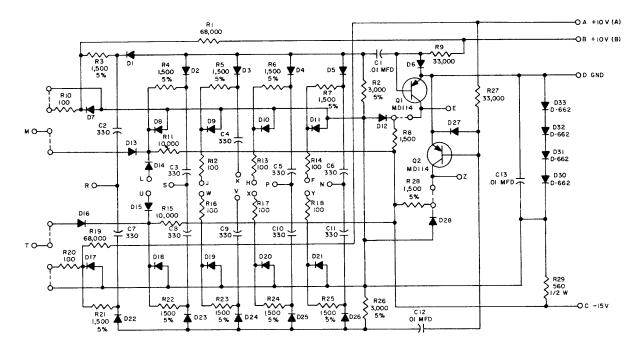

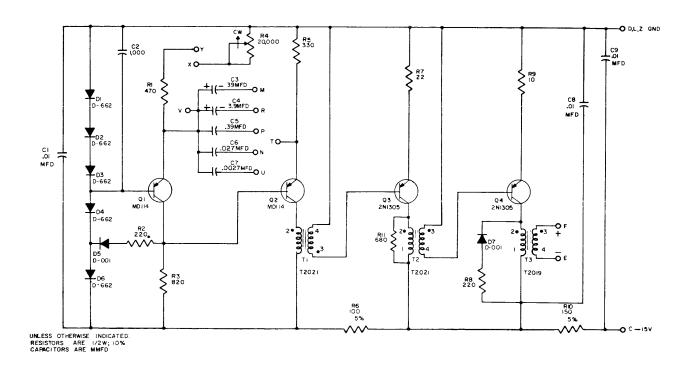

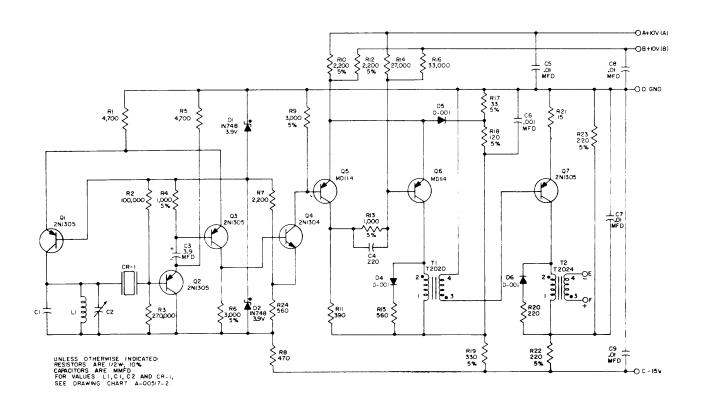

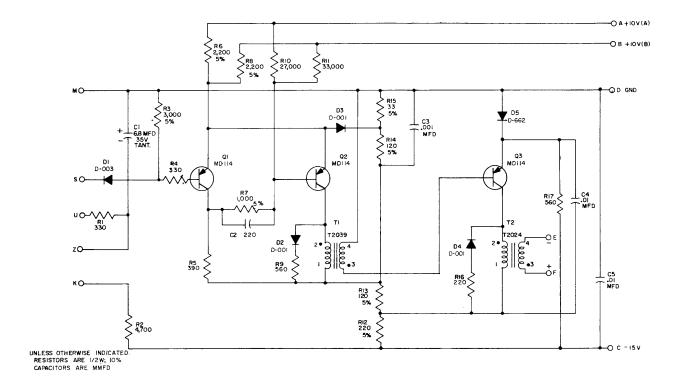

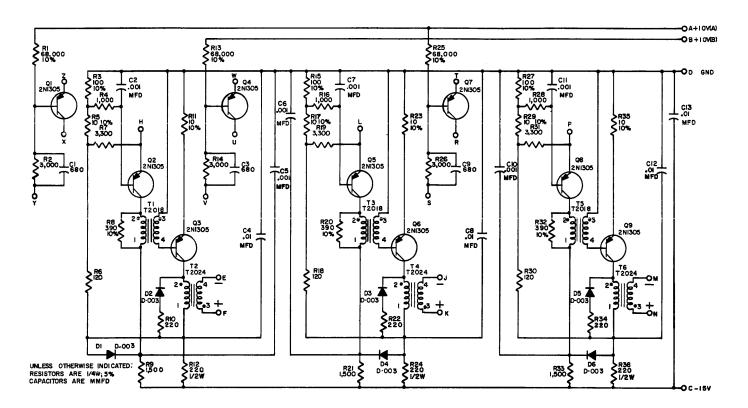

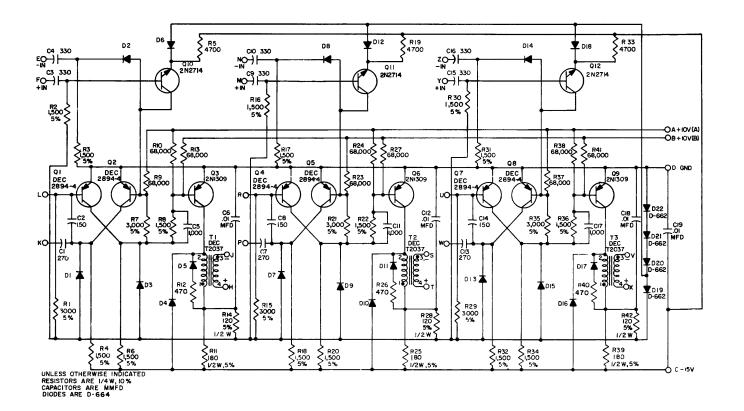

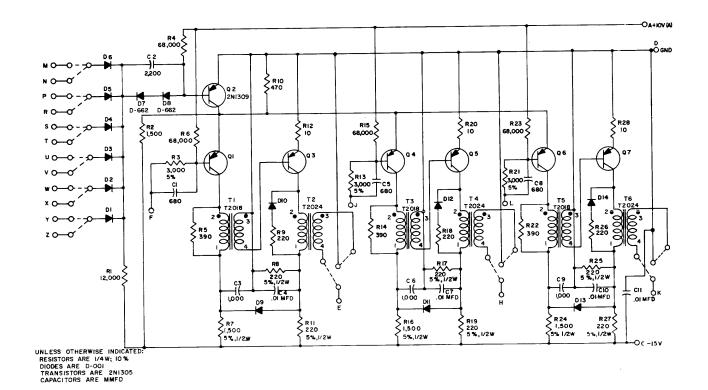

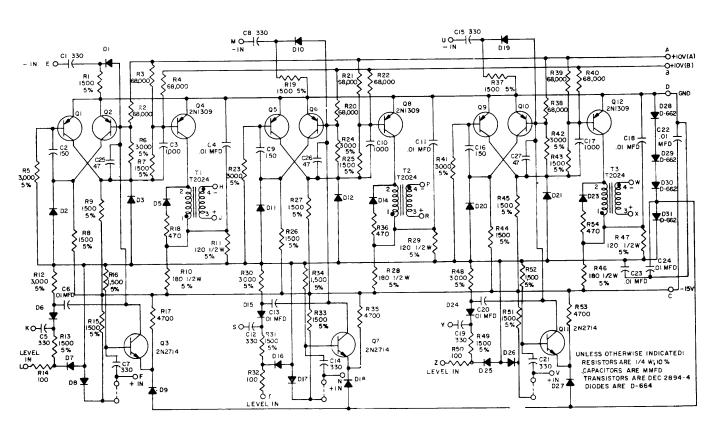

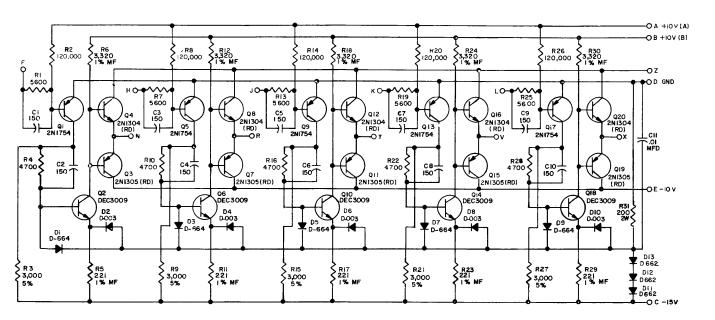

|         | Power Supply and Control                             | 10-2 |

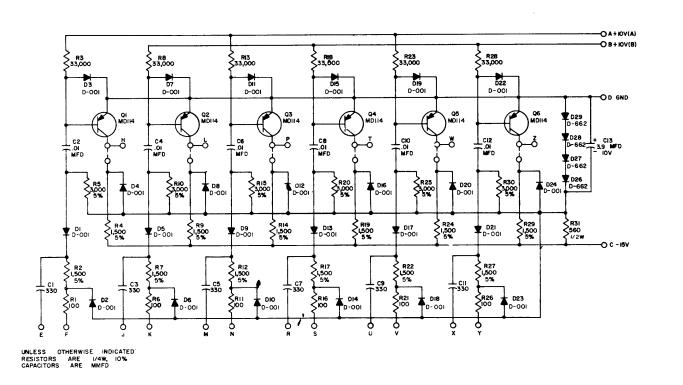

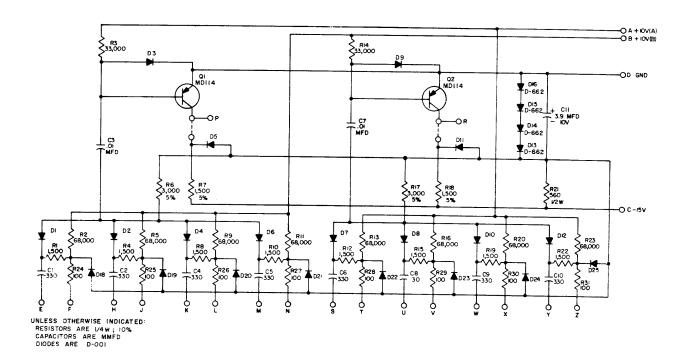

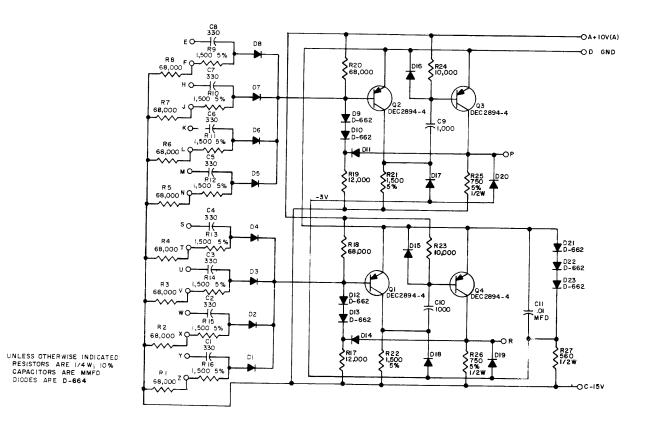

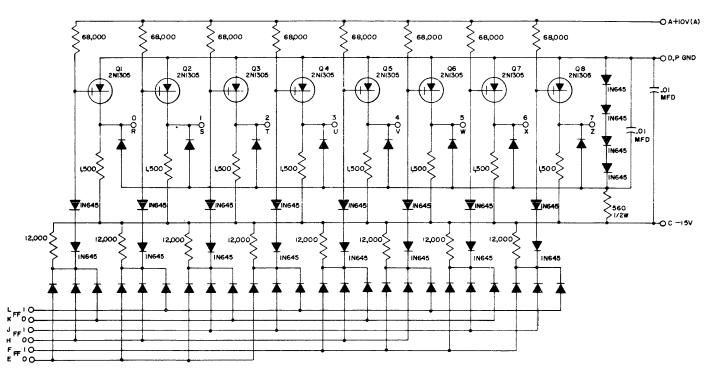

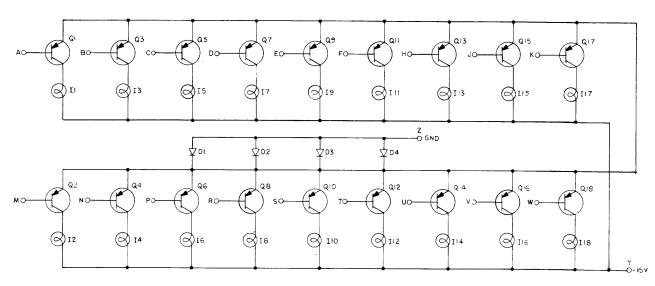

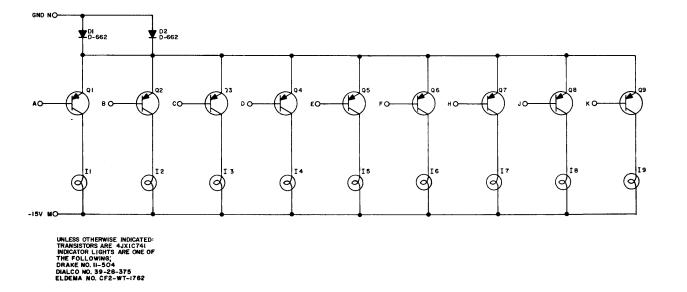

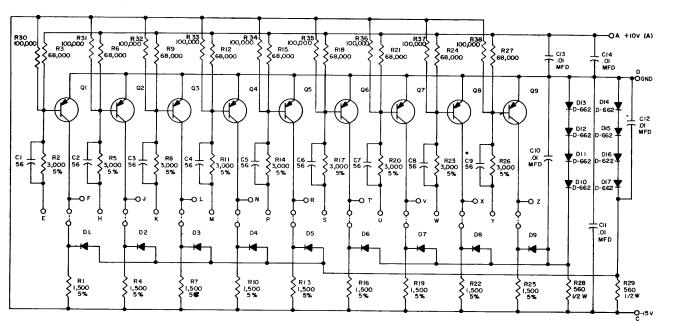

|         | System Modules                                       | 10-2 |

|         | Logic                                                | 10-4 |

|         | Module Location and Wiring                           | 10-5 |

|         | TABLES                                               |      |

| Table   |                                                      |      |

| 3-1     | Read-Write Switch Gating                             | 3-10 |

| 4-1     | Teletype Control Interface with Processor            | 4-3  |

| 4-2     | Analog-to-Digital Converter Interface with Processor | 4-8  |

| 4-3     | Characteristics of the 137                           | 4-9  |

| 6-1     | Input Signals                                        | 6-2  |

| 6-2     | Output Signals                                       | 6-5  |

| 8-1     | Operator Console Controls and Indicators             | 8-2  |

| 8-2     | Teletype Controls and Indicators                     | 8-6  |

| 8-3     | Readin Mode Loader Program                           | 8-9  |

| 8-4     | Teletype Code                                        | 8-15 |

| 9-1     | Maintenance Equipment                                | 9-1  |

| 9-2     | Maintenance Controls and Indicators                  | 9-3  |

| 9-3     | Type 779 Power Supply Outputs                        | 9-6  |

| 9-4     | Maindec Programs Used in Marginal Checking           | 9-10 |

| 9-5     | Analog-Digital Number Conversion                     | 9-15 |

| 9-6     | Digital-to-Analog Converter Adjustment Program       | 9-19 |

| 9-7     | Suggested Spare Semiconductors                       | 9-35 |

# TABLES (continued)

| Table             |                                                                                                    | Page  |

|-------------------|----------------------------------------------------------------------------------------------------|-------|

| 9-8               | Suggested Miscellaneous Spare Parts                                                                | 9-36  |

| 9-9               | Suggested Spare Parts for Type 50 Magnetic Tape Transports                                         | 9-37  |

| × .               |                                                                                                    |       |

|                   | ILLUSTRATIONS                                                                                      |       |

| Figure            |                                                                                                    |       |

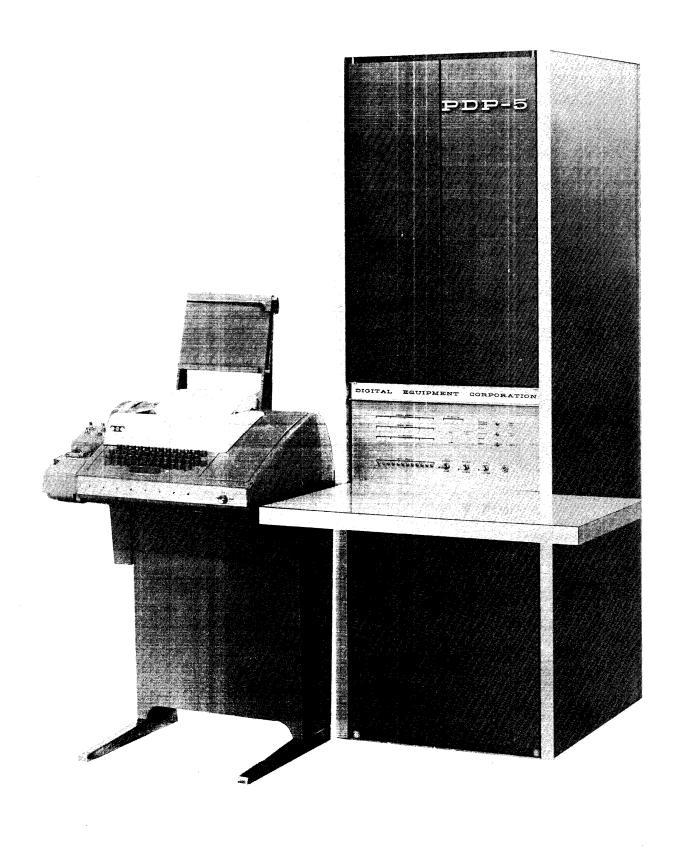

| 1-1               | A Standard PDP-5 System                                                                            | xvi   |

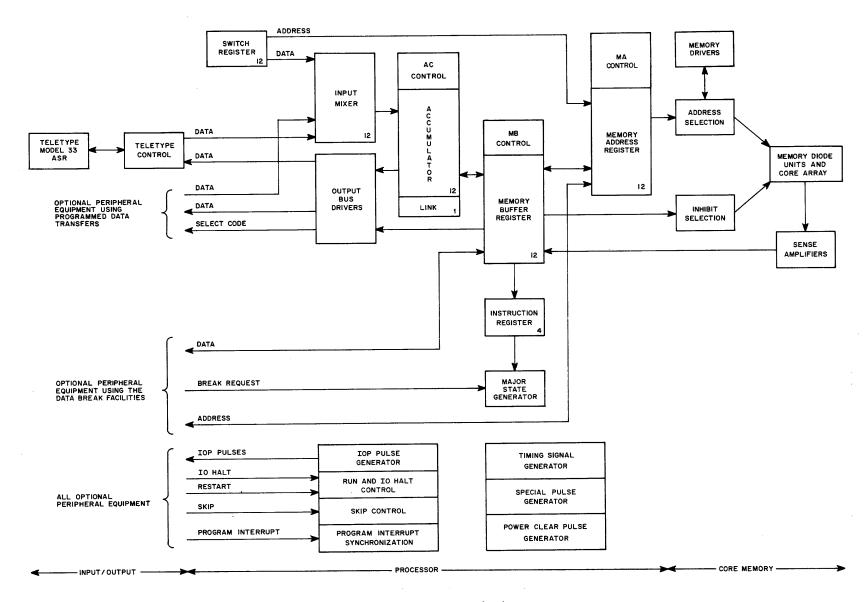

| 1-2               | Simplified Block Diagram                                                                           | 1-2   |

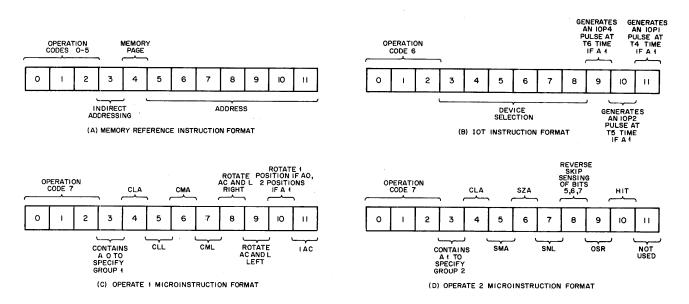

| 1-3               | Instruction Formats                                                                                | 1-7   |

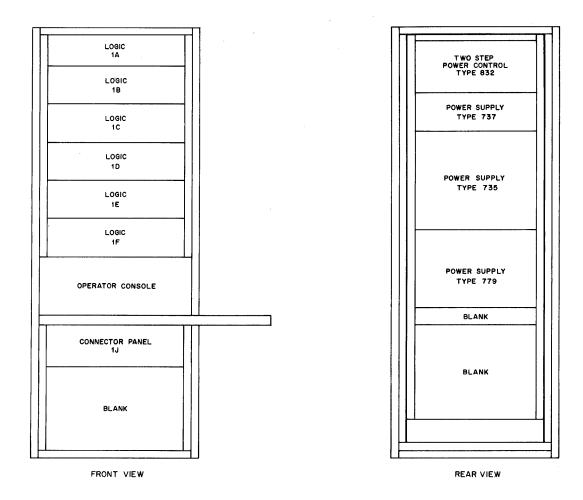

| 1-4               | Component Locations                                                                                | 1-12  |

| 1-5               | Logic Symbols                                                                                      | 1-15  |

| 2-1               | Timing Diagram                                                                                     | 2-4   |

| 3-1               | Core Memory Block Diagram (During Writing)                                                         | 3-3   |

| 3-2               | Core Memory Drive System Equivalent Circuit                                                        | 3-4   |

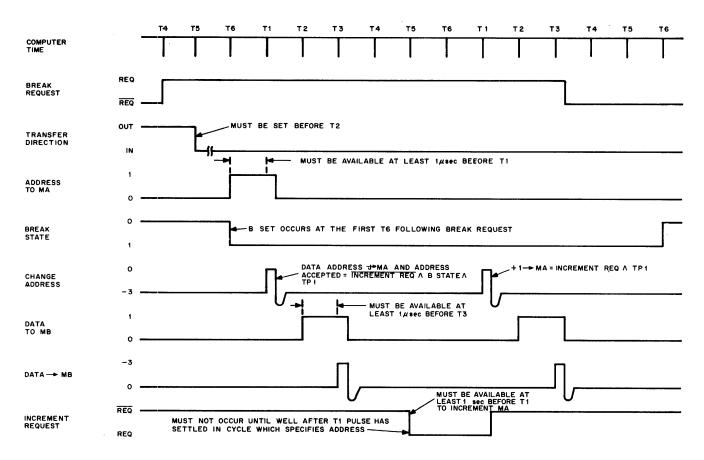

| 5-1               | Data Break Timing                                                                                  | 5-16  |

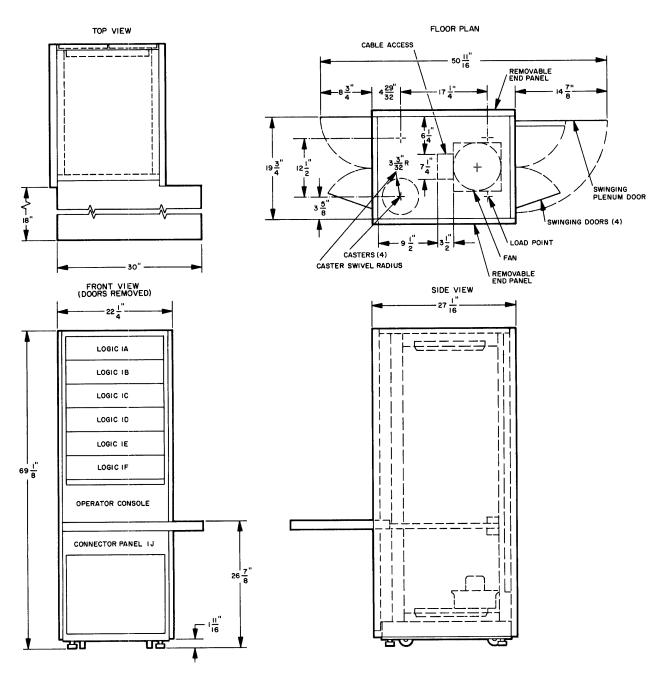

| 7-1               | Installation Outline Drawing                                                                       | 7-2   |

| 7-2               | Installation Connections                                                                           | 7-6   |

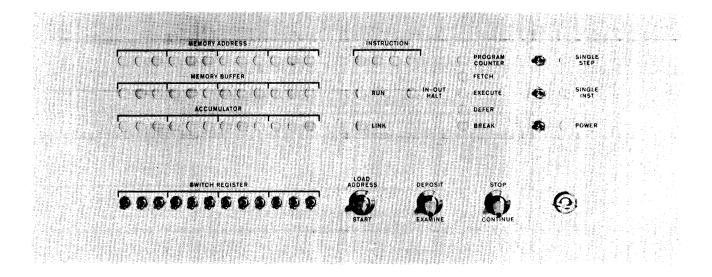

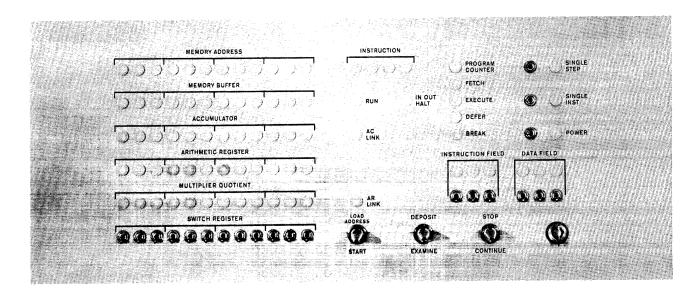

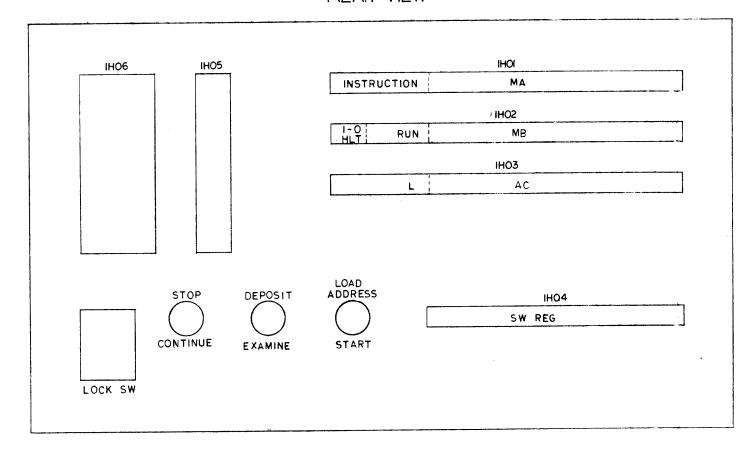

| 8-1               | Standard Operator Console                                                                          | 8-1   |

| 8-2               | Operator Console with Type 153 Automatic Multiply and Divide and Type 154 Memory Extension Control | 8-2   |

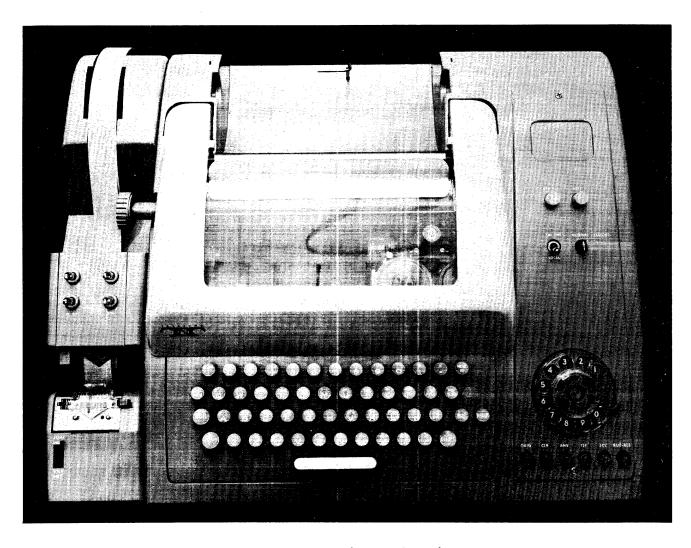

| 8-3               | Teletype Console                                                                                   | 8-6   |

|                   | DRAWINGS                                                                                           |       |

| D                 |                                                                                                    |       |

| Drawing<br>DS 725 |                                                                                                    | 10.7  |

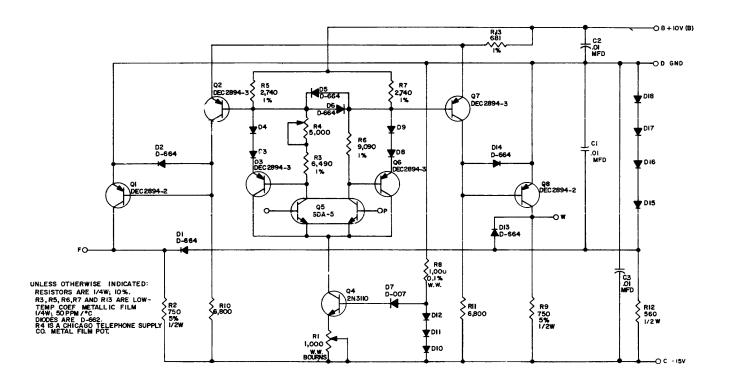

| RS-735            | Power Supply                                                                                       | 10-7  |

| RS-1701           | Power Supply Control                                                                               | 10-7  |

| RS-737            | Power Supply                                                                                       | 10-9  |

| RS-779            | Power Supply                                                                                       | 10-9  |

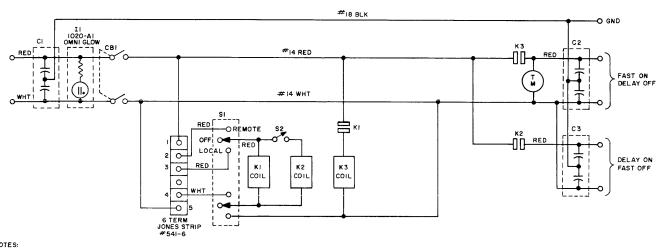

| RS-832            | Two Step Power Control                                                                             | 10-11 |

# DRAWINGS (continued)

| Drawing |                                    | Page  |

|---------|------------------------------------|-------|

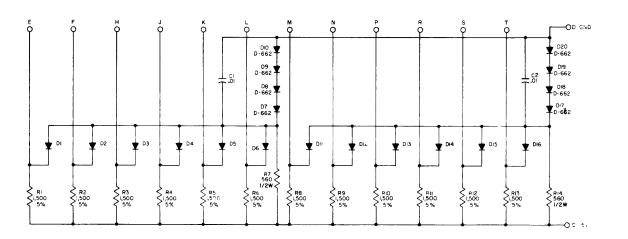

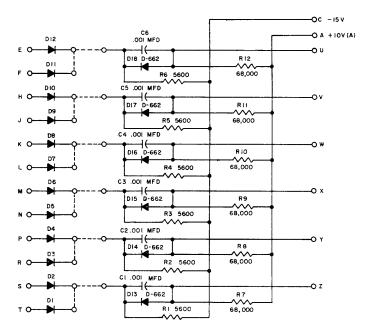

| RS-1000 | Clamped Load Resistors             | 10-11 |

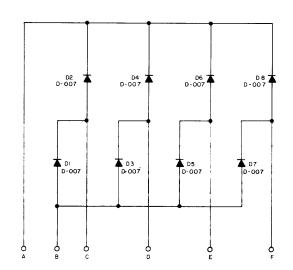

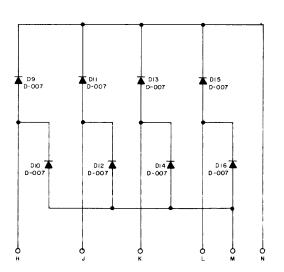

| RS-1011 | Diode                              | 10-13 |

| RS-1020 | Memory Diode Unit                  | 10-13 |

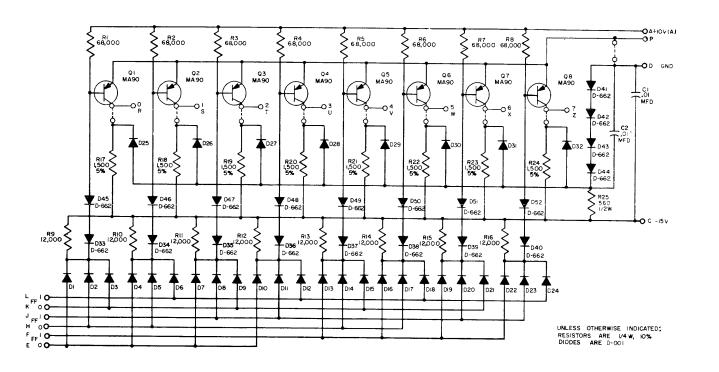

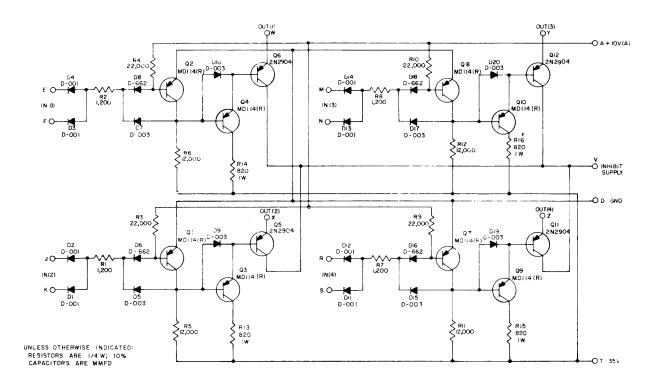

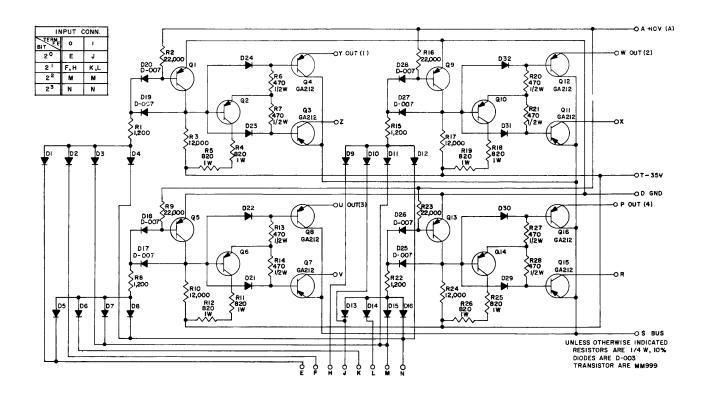

| RS-1151 | Binary-to-Octal Decoder            | 10-15 |

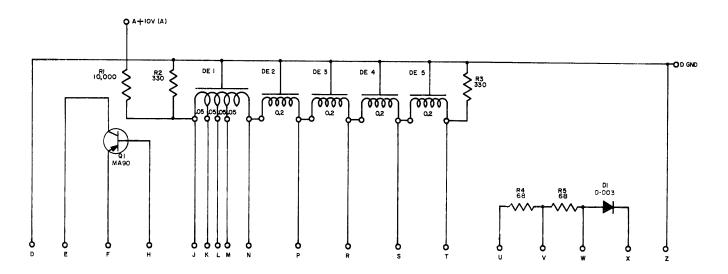

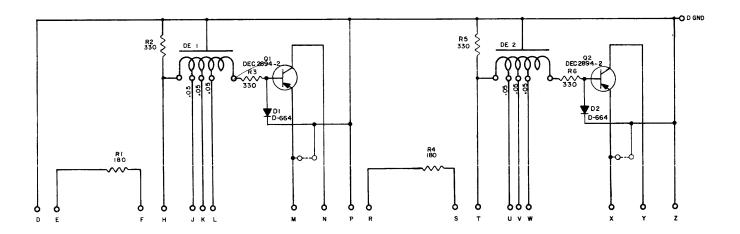

| RS-1310 | Delay Line                         | 10-15 |

| RS-1311 | Delay Line                         | 10-17 |

| RS-1406 | Crystal Clock                      | 10-17 |

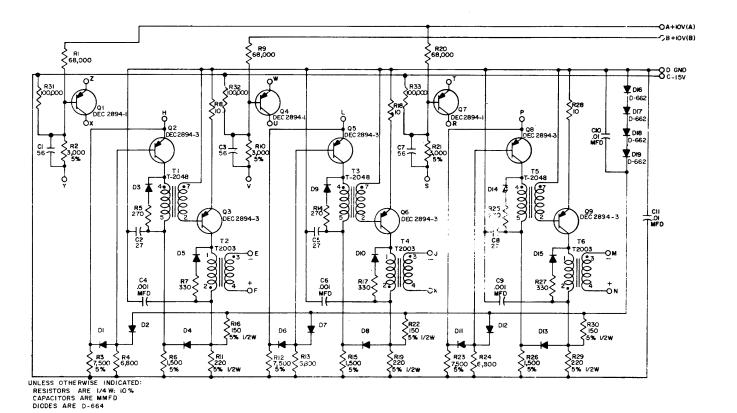

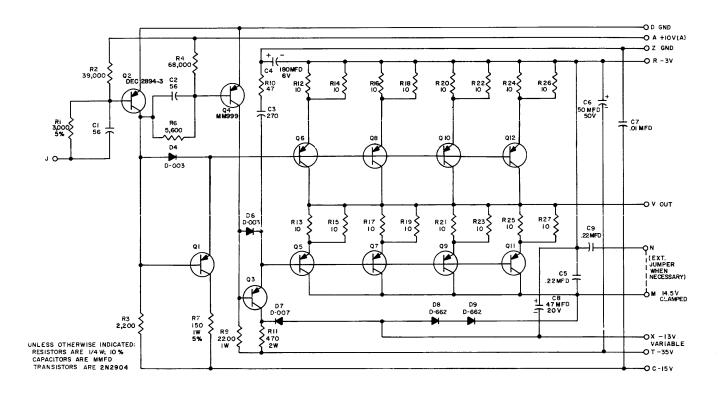

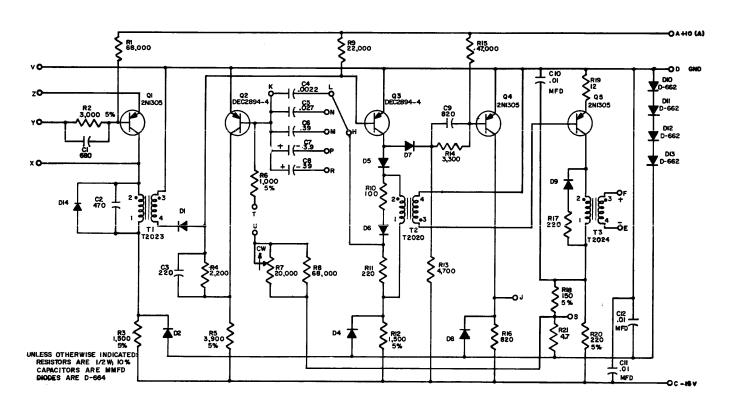

| RS-1571 | Dual Sense Amplifier               | 10-19 |

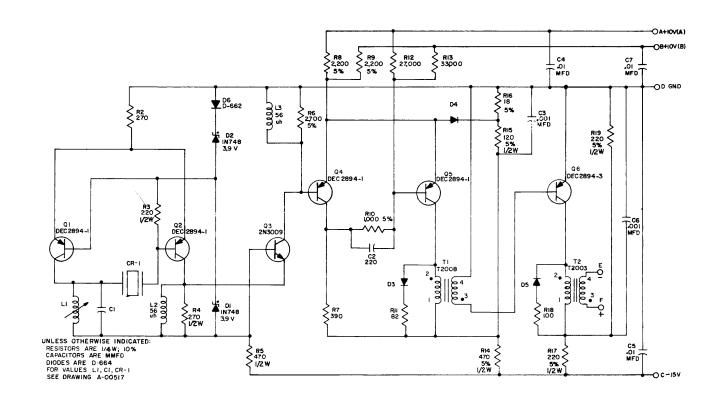

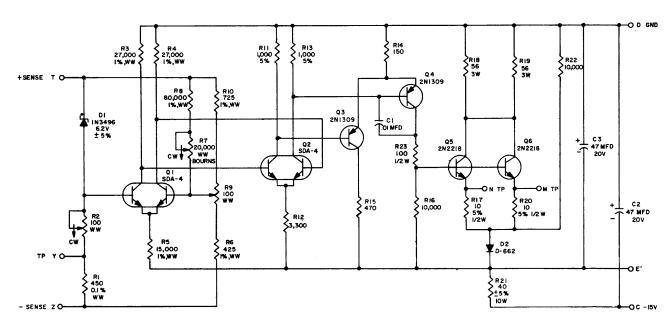

| RS-1572 | Difference Amplifier               | 10-21 |

| RS-1574 | 12-Bit Digital-to-Analog Converter | 10-21 |

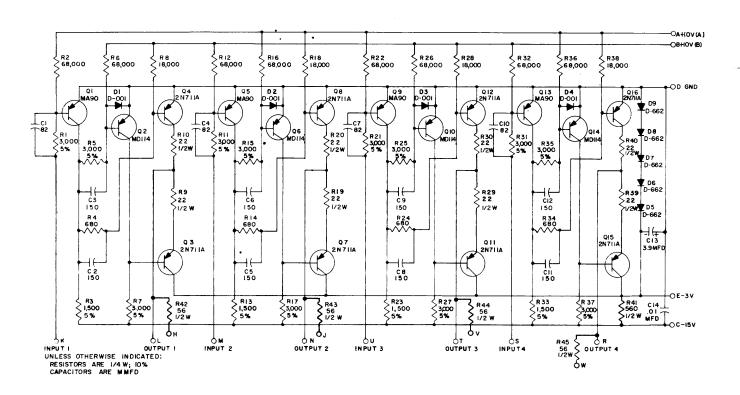

| RS-1607 | Pulse Amplifier                    | 10-23 |

| RS-1684 | Bus Driver                         | 10-23 |

| RS-1685 | Bus Driver                         | 10-25 |

| RS-1704 | -10V Precision Power Supply        | 10-25 |

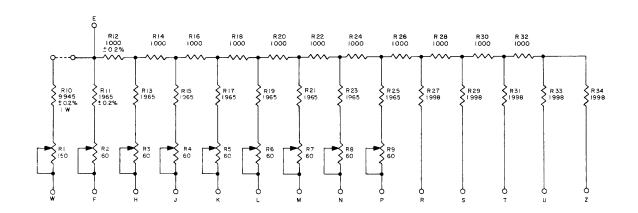

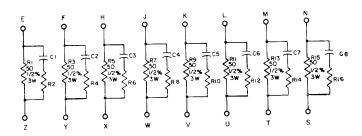

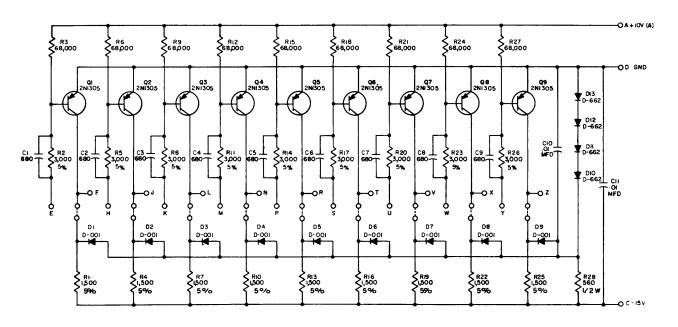

| RS-1976 | Resistor Board                     | 10-27 |

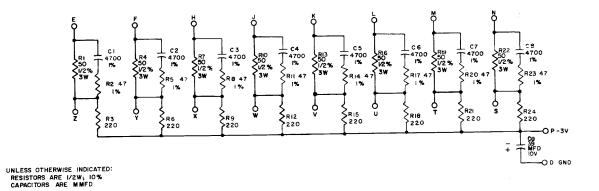

| RS-1978 | Resistor Board                     | 10-27 |

| RS-1982 | Inhibit Driver                     | 10-29 |

| RS-1987 | Read-Write Switch                  | 10-29 |

| RS-1989 | Memory Driver                      | 10-31 |

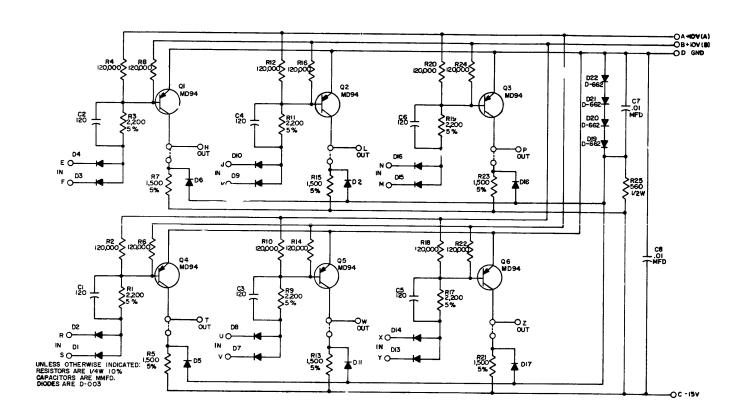

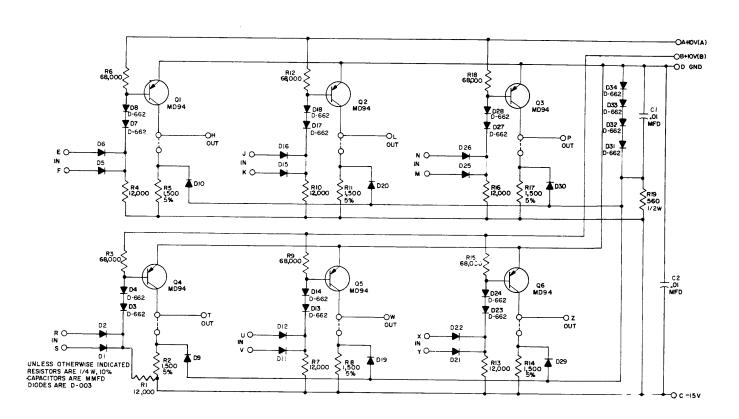

| RS-4102 | Inverter                           | 10-31 |

| RS-4106 | Inverter                           | 10-33 |

| RS-4111 | Diode                              | 10-33 |

| RS-4112 | Negative Diode NOR                 | 10-35 |

| RS-4113 | Diode                              | 10-35 |

| RS-4114 | Negative Diode NOR                 | 10-37 |

| RS-4115 | Positive Diode NOR                 | 10-37 |

| RS-4116 | Diode                              | 10-39 |

| RS-4117 | Positive Diode NOR                 | 10-39 |

| RS-4123 | Negative Capacitor Diode Gate      | 10-41 |

| RS-4127 | Pulse Inverter                     | 10-41 |

# DRAWINGS (continued)

| Drawing |                                     | <u>Page</u> |

|---------|-------------------------------------|-------------|

| RS-4129 | Pulse Inverter                      | 10-43       |

| RS-4130 | Positive Capacitor-Diode Gate       | 10-43       |

| RS-4151 | Binary-to-Octal Decoder             | 10-45       |

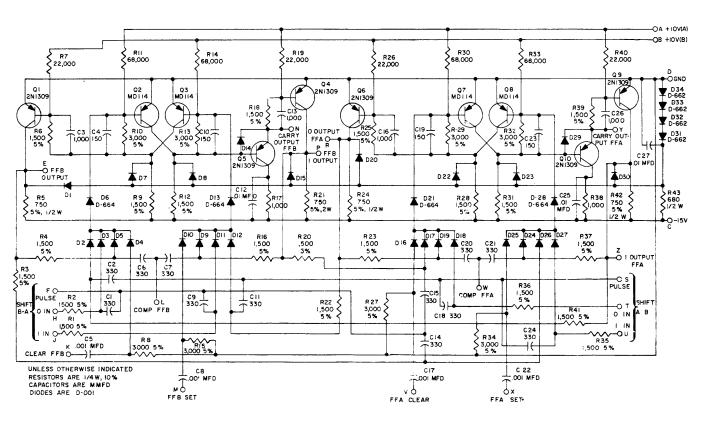

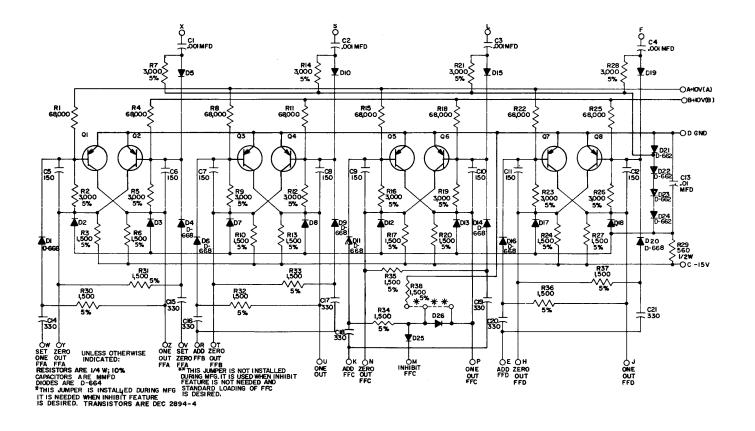

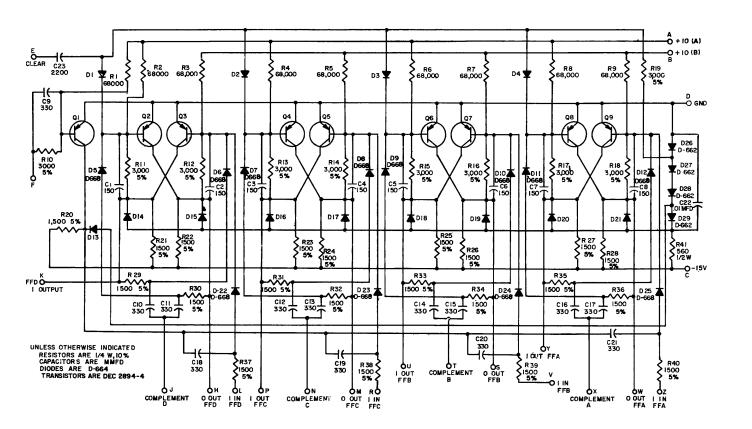

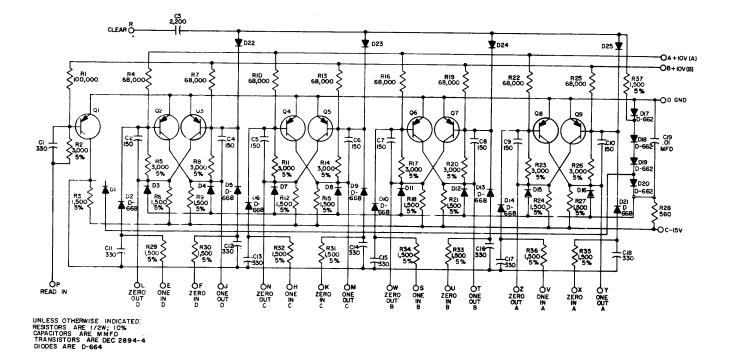

| RS-4205 | Dual Flip-Flop                      | 10-45       |

| RS-4206 | Triple Flip-Flop                    | 10-47       |

| RS-4215 | 4-Bit Counter                       | 10-49       |

| RS-4217 | 4-Bit Counter                       | 10-49       |

| RS-4218 | Quadruple Flip-Flop                 | 10-51       |

| RS-4220 | 8-Bit Buffer Register               | 10-51       |

| RS-4225 | 8-Bit BCD or Binary Counter         | 10-53       |

| RS-4231 | Quadruple Flip-Flop                 | 10-55       |

| RS-4301 | Delay (One Shot)                    | 10-57       |

| RS-4303 | Integrating Single Shot             | 10-57       |

| RS-4401 | Variable Clock                      | 10-59       |

| RS-4407 | Crystal Clock                       | 10-59       |

| RS-4410 | Pulse Generator                     | 10-61       |

| RS-4554 | Dual Sense Amplifier                | 10-63       |

| RS-4603 | Pulse Amplifier                     | 10-65       |

| RS-4604 | Pulse Amplifier                     | 10-65       |

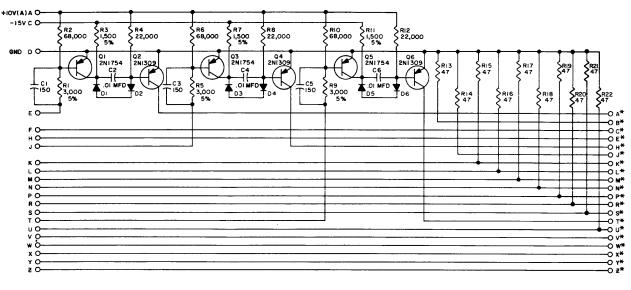

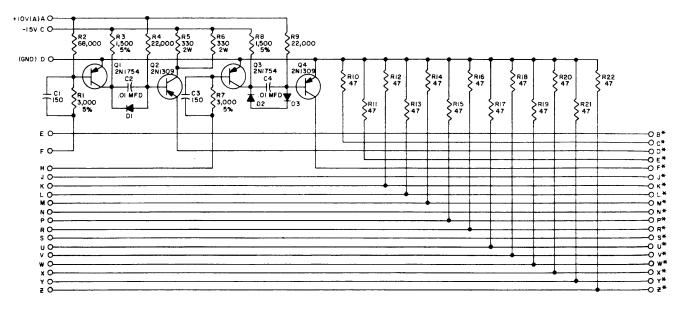

| RS-4605 | Pulse Amplifier                     | 10-67       |

| RS-4606 | Pulse Amplifier                     | 10-67       |

| RS-4678 | Level Amplifier                     | 10-69       |

| RS-4706 | Teletype Incoming Line Unit         | 10-71       |

| RS-4707 | Teletype Transmitter                | 10-73       |

| RS-4801 | 22-Pin Plug Adapter with Bus Driver | 10-75       |

| RS-4802 | 22-Pin Plug Adapter with Bus Driver | 10-75       |

| RS-4903 | 18-Lamp Bracket                     | 10-77       |

| RS-4904 | 9-Lamp Bracket                      | 10-77       |

| RS-6102 | Inverter                            | 10-79       |

# DRAWINGS (continued)

| Drawing               |                                                       | Page           |

|-----------------------|-------------------------------------------------------|----------------|

| FD-D-5-0-2            | Flow Diagram                                          | 10-81          |

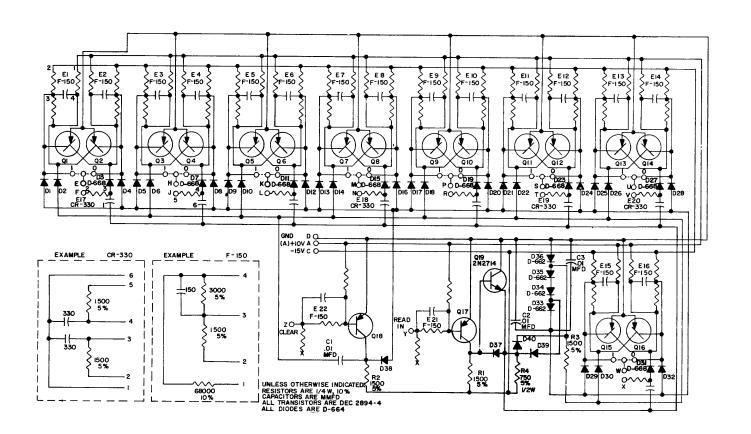

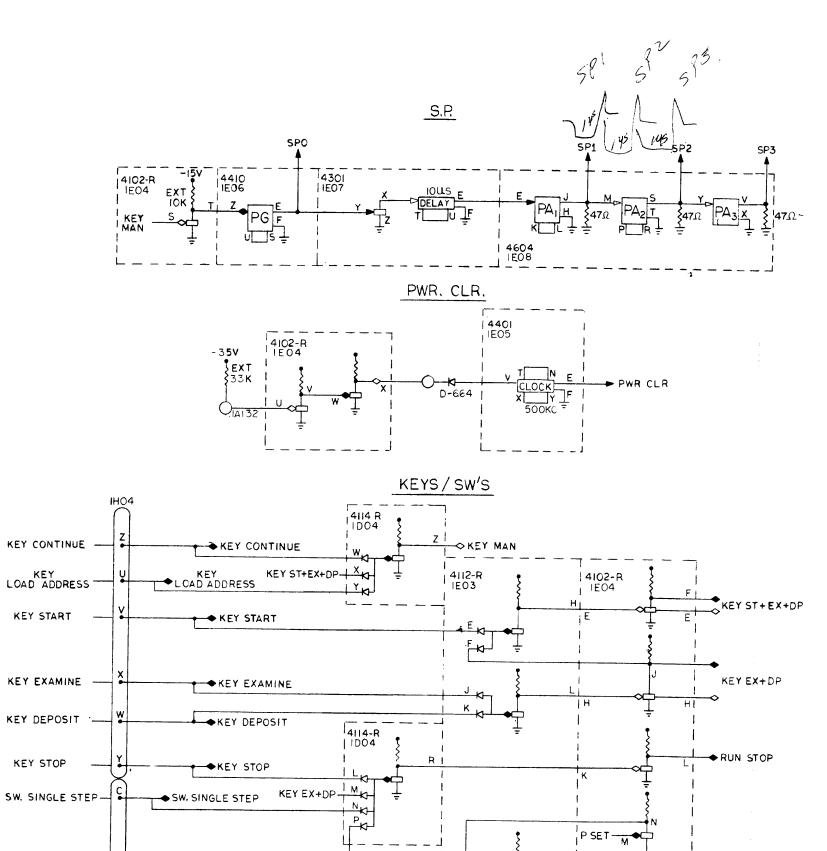

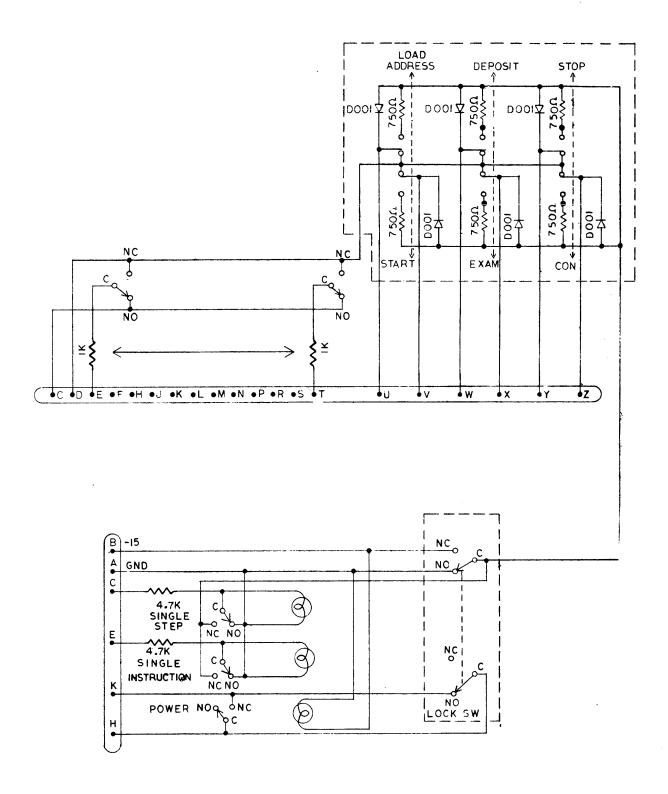

| BS-D-5-0-5            | Keys, Switches, Run, I/O Halt, SP's, Power Clear      | 10-83          |

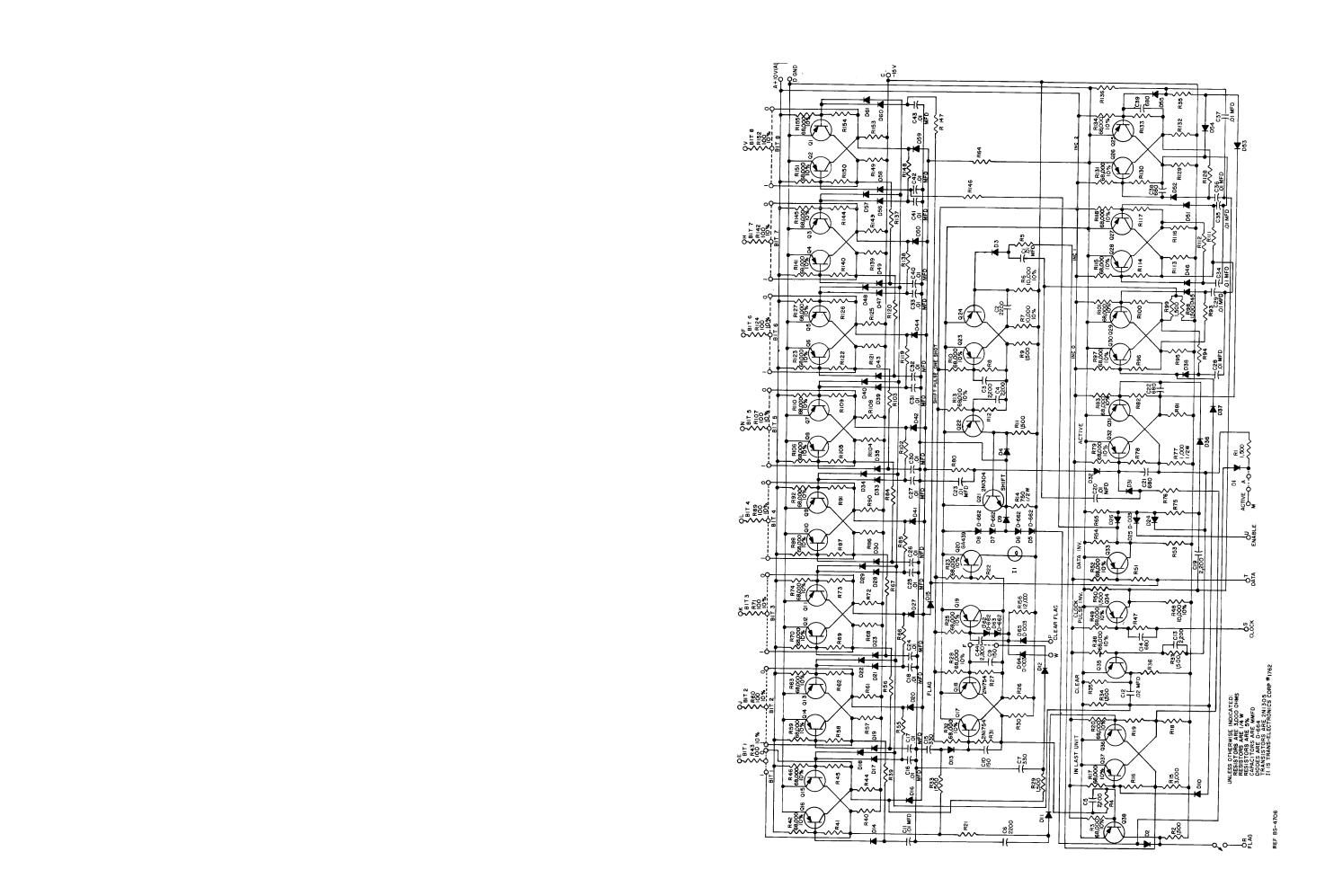

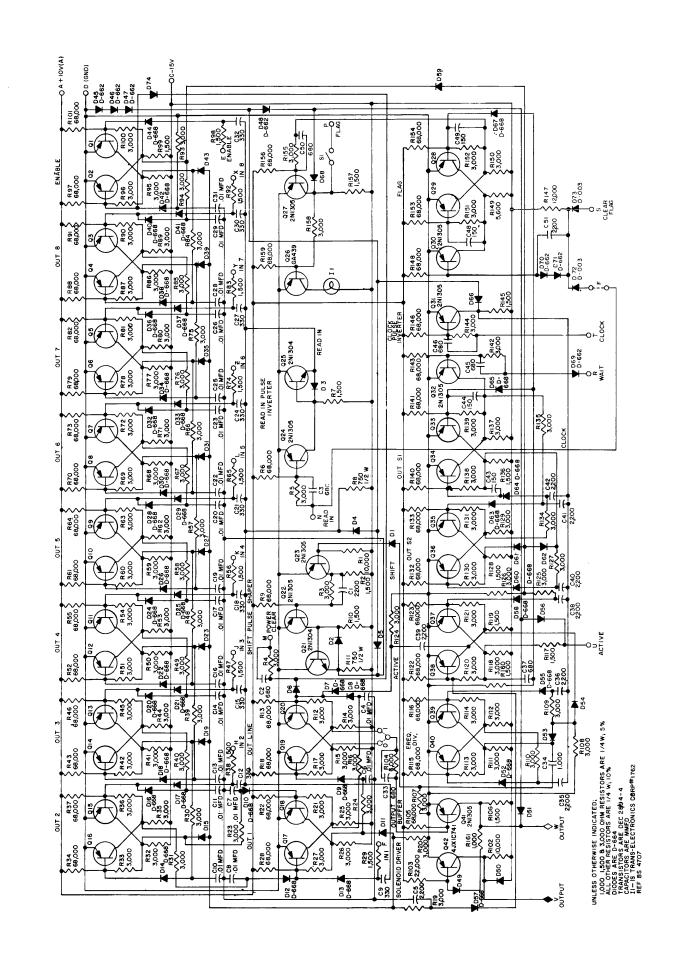

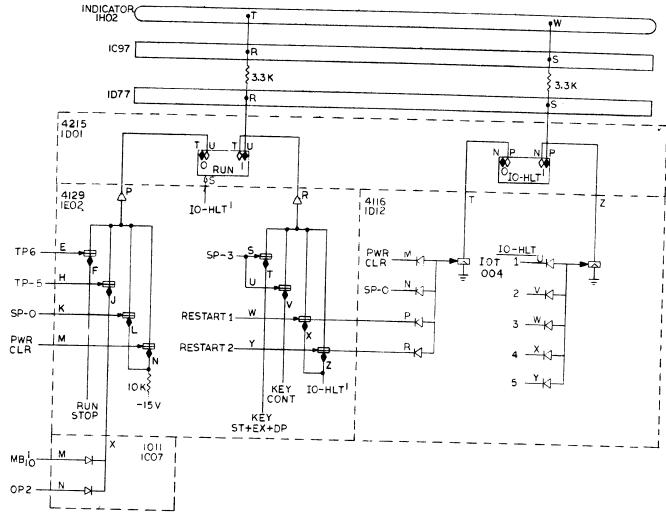

| BS-D-5-0-6            | Major States, Instruction Register, IOP's             | 10-85          |

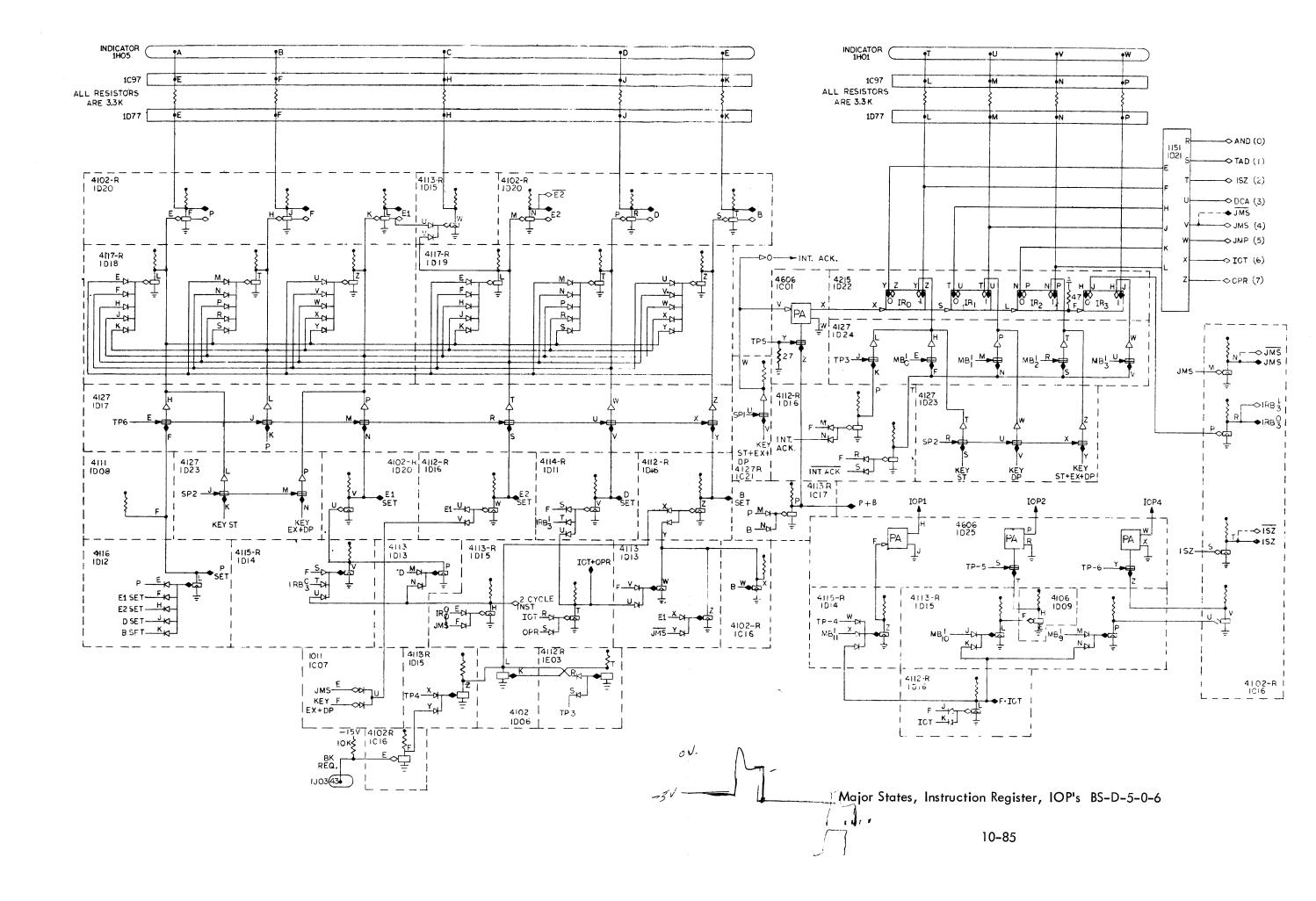

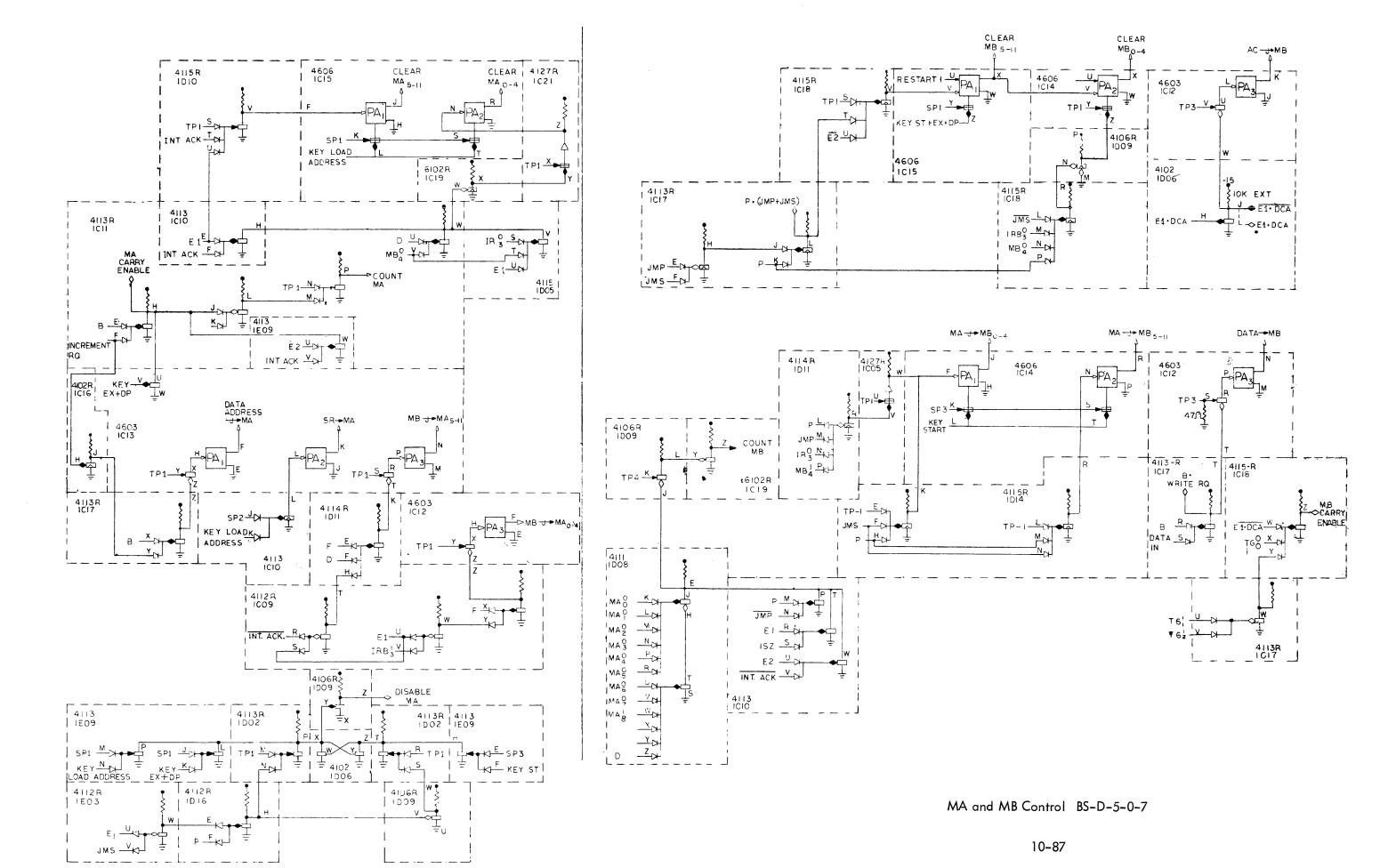

| BS-D-5-0-7            | MA and MB Control                                     | 10-87          |

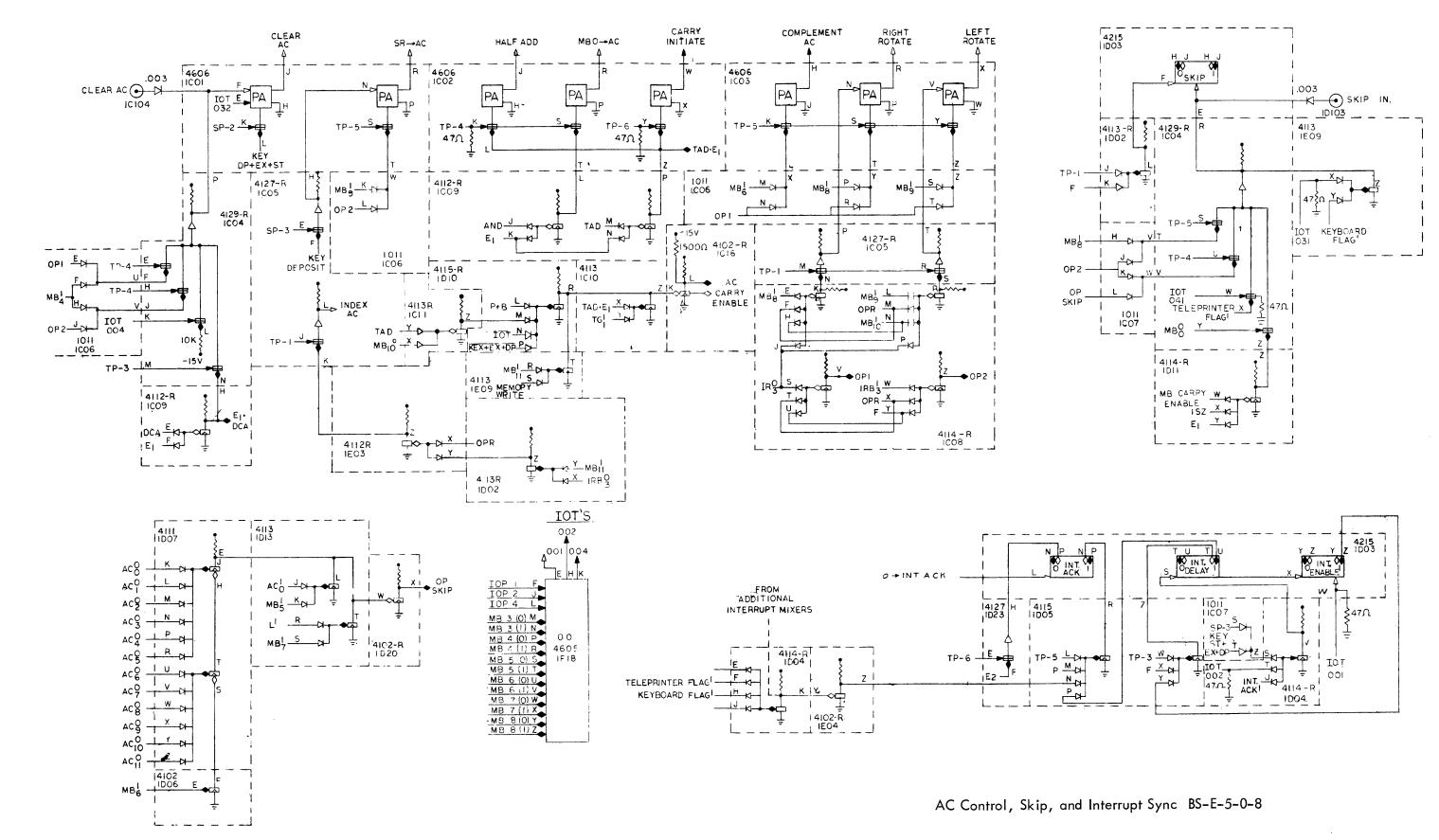

| BS-E-5-0-8            | AC Control, Skip, and Interrupt Sync                  | 10-89          |

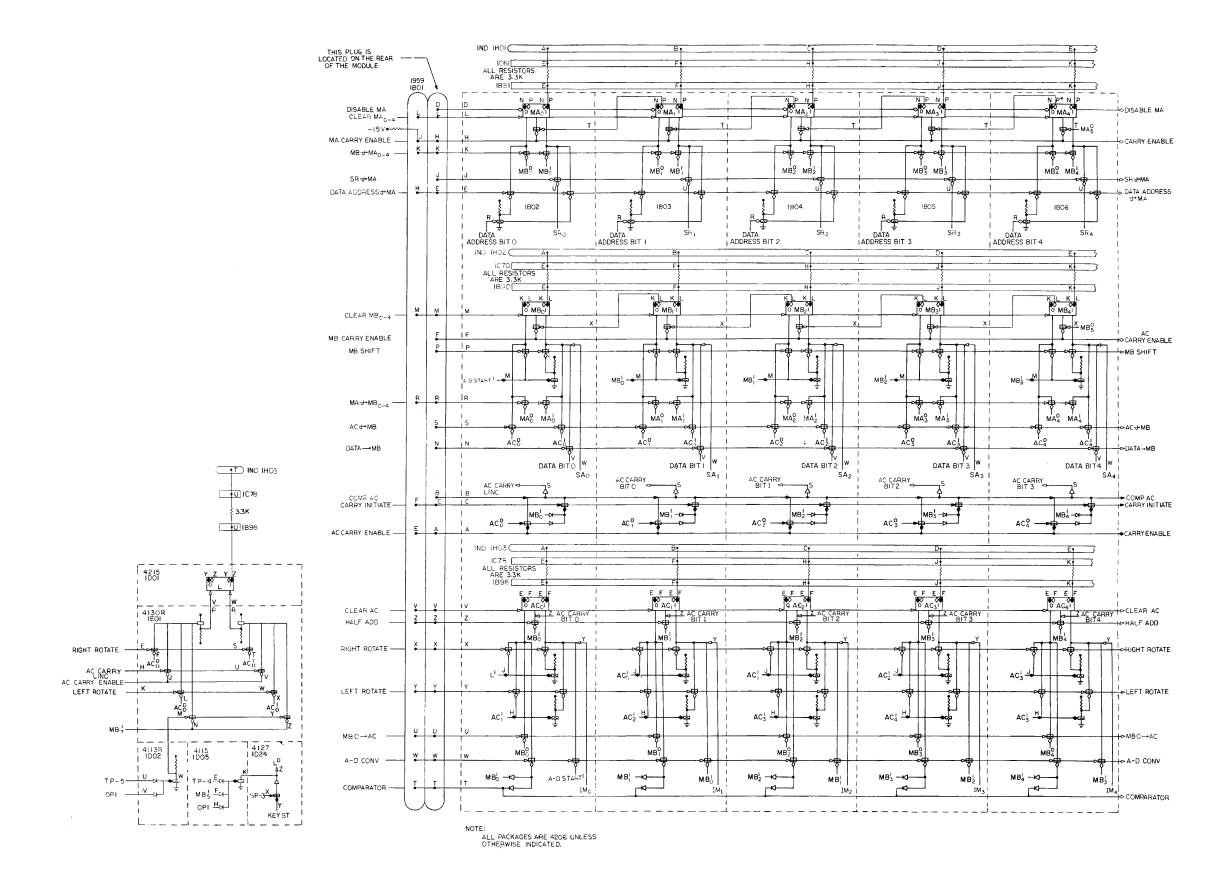

| BS-E-5-0-9            | Link, AC, MB, MA (Sheet 1 of 2)                       | 10-91          |

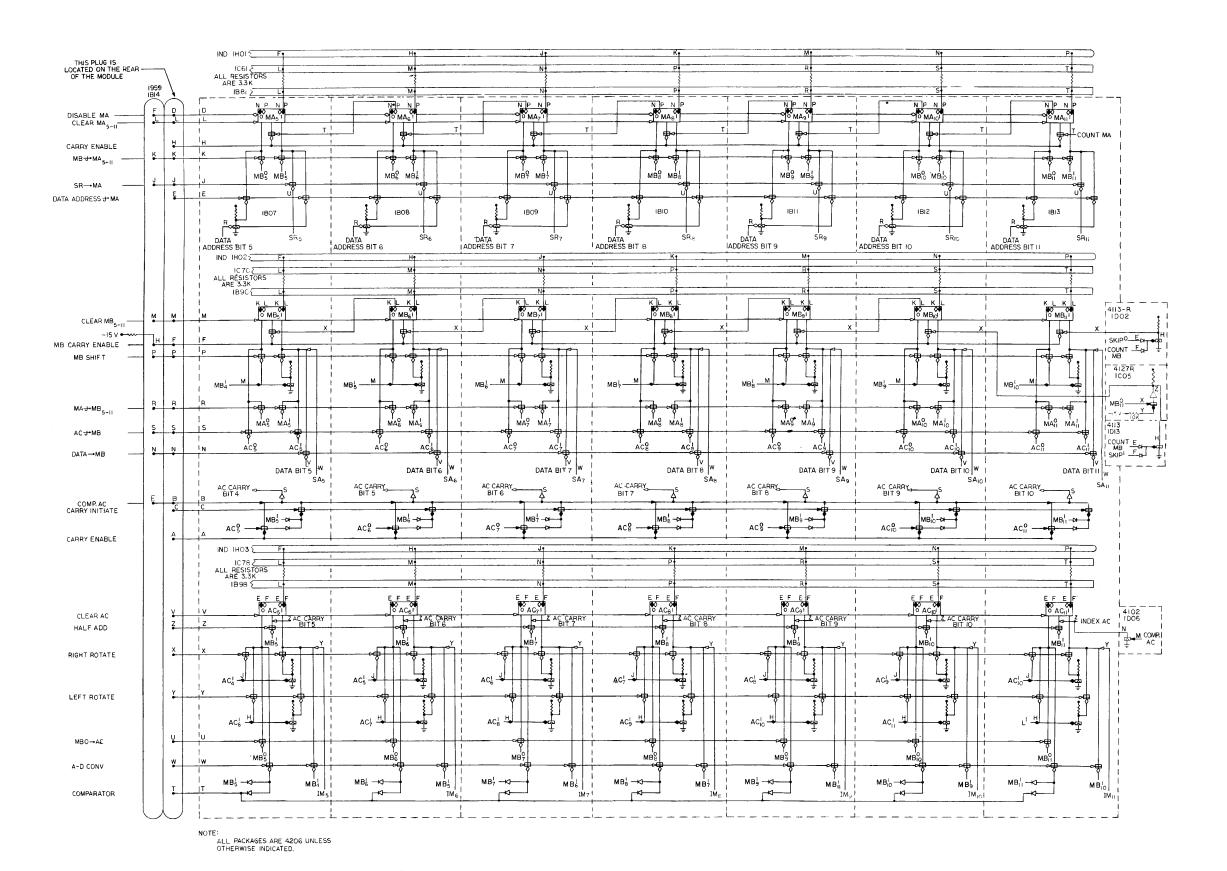

| BS-E-5-0-9            | Link, AC, MB, MA (Sheet 2 of 2)                       | 10-93          |

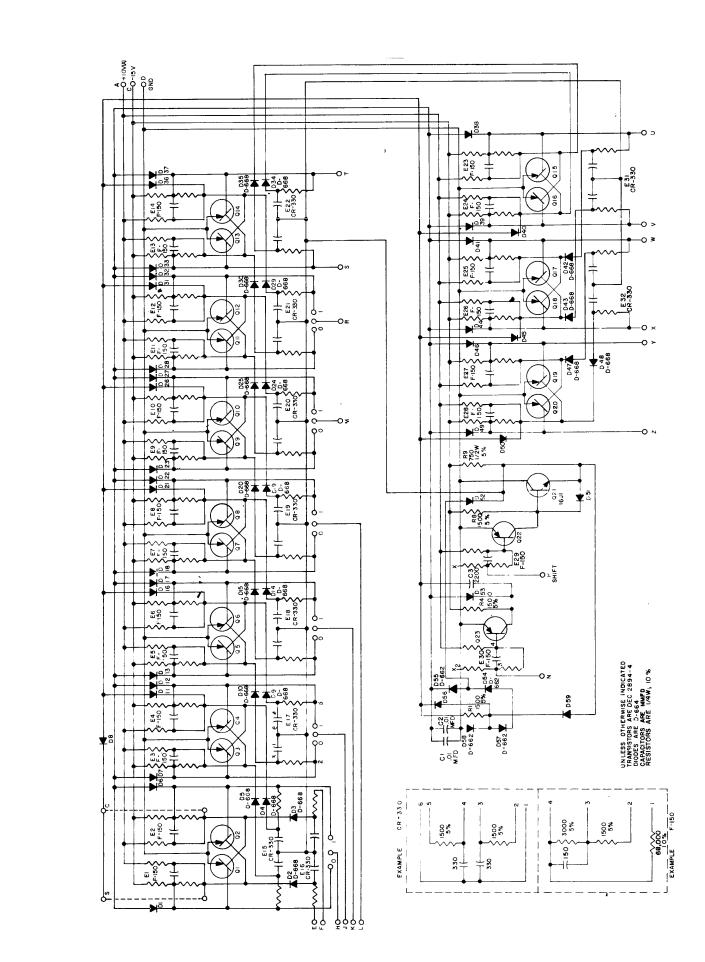

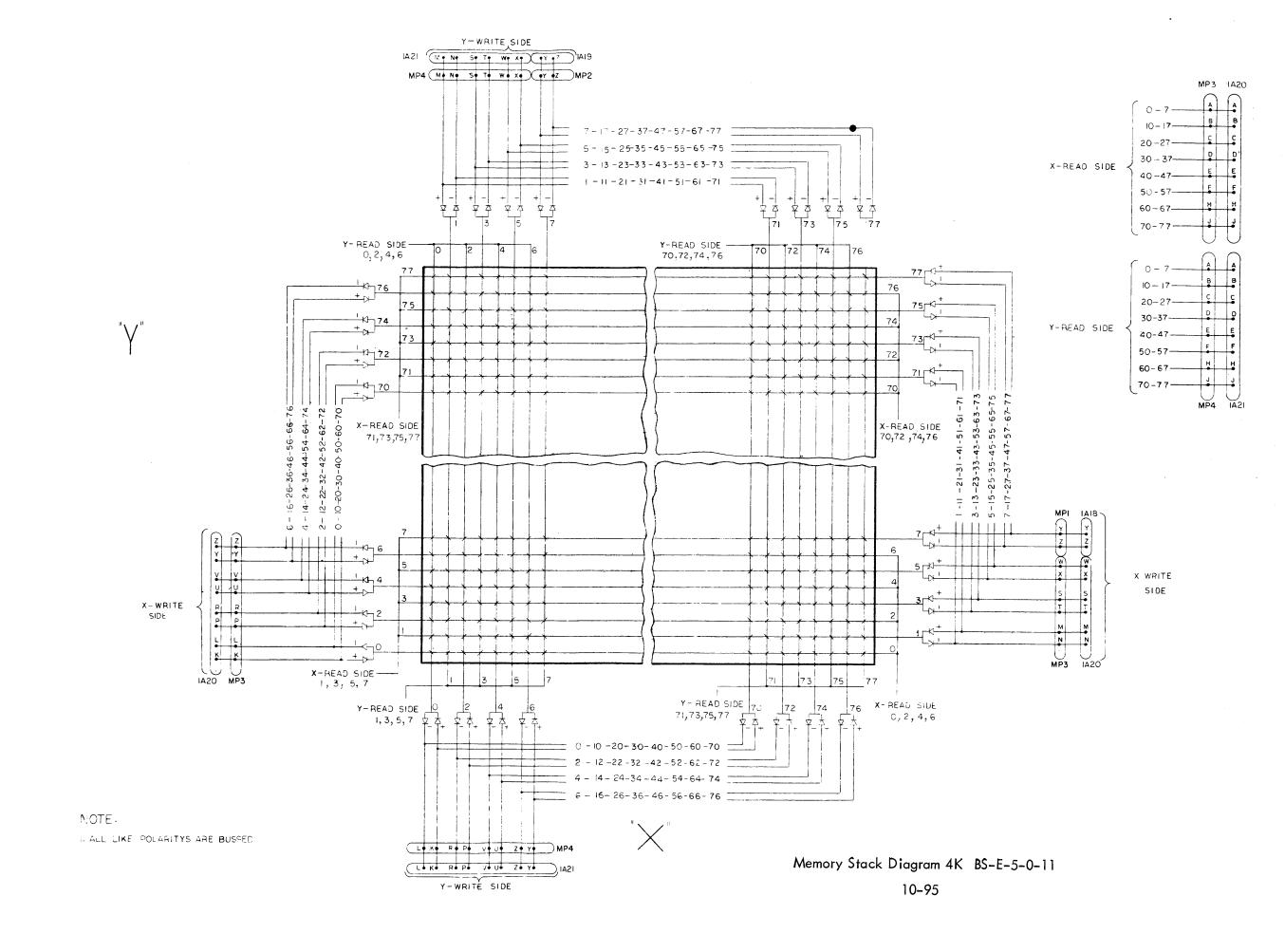

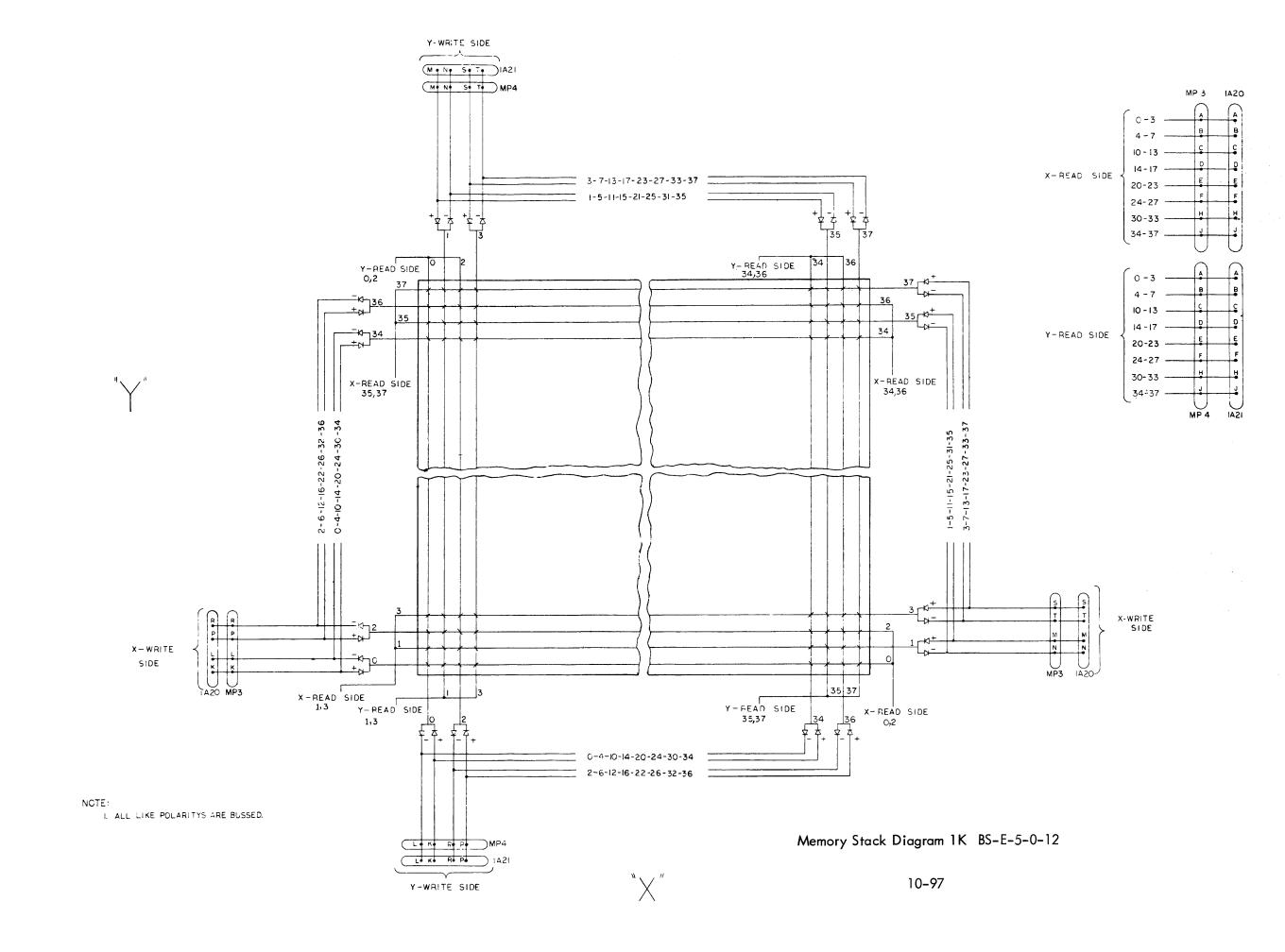

| BS-E-5-0-11           | Memory Stack Diagram 4K                               | 10-95          |

| BS-E-5-0-12           | Memory Stack Diagram 1K                               | 10-97          |

| BS-D-5-0-14           | Input Mixer                                           | 10-99          |

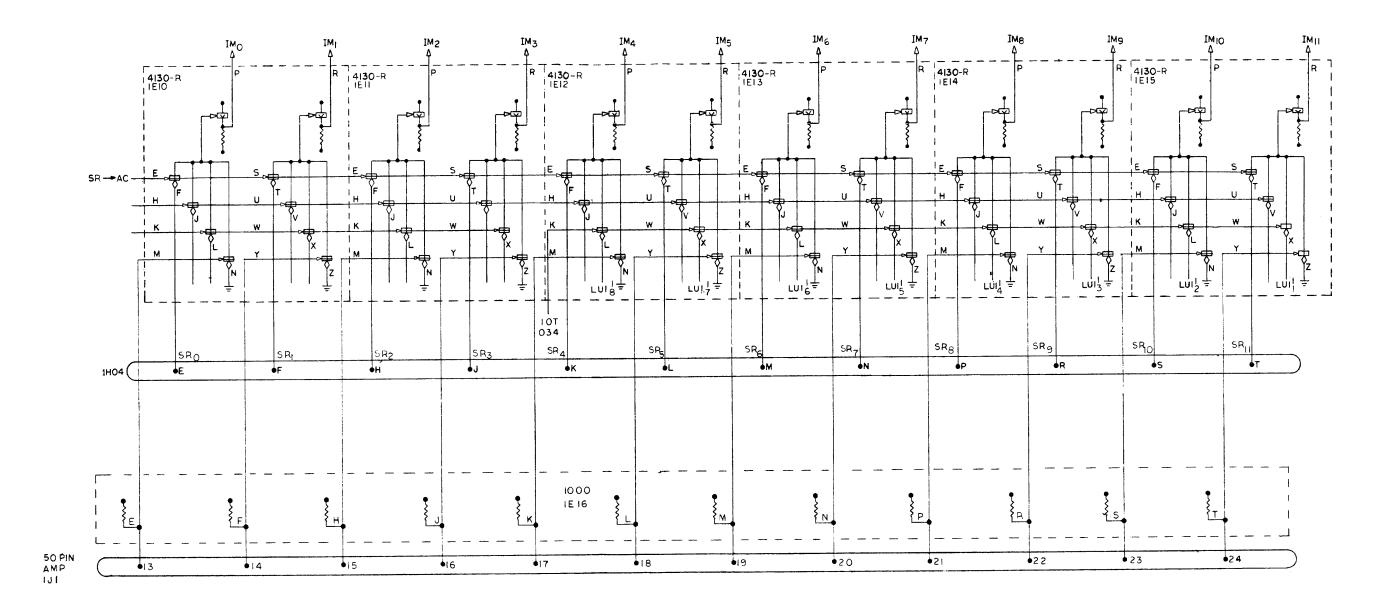

| BS-D-5-0-16           | Memory "X" and "Y" Selection                          | 10-101         |

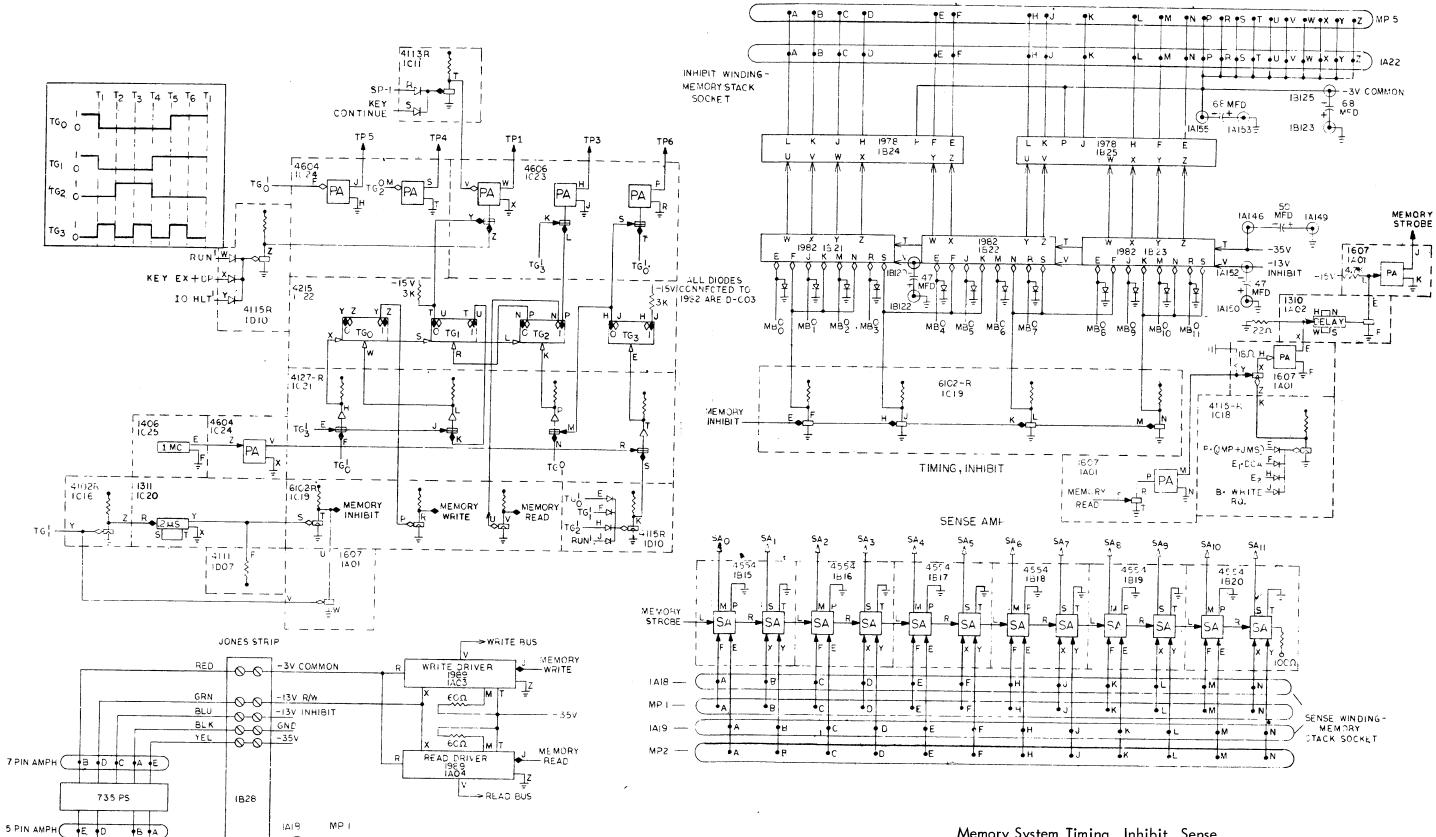

| BS-D-5-0-17           | Memory System Timing, Inhibit, Sense Amplifier Output | 10-103         |

| BS-D-5-0-18           | Keyboard/Printer Control                              | 10-105         |

| BS-D-5-0-31           | Output Bus Drivers                                    | 10-107         |

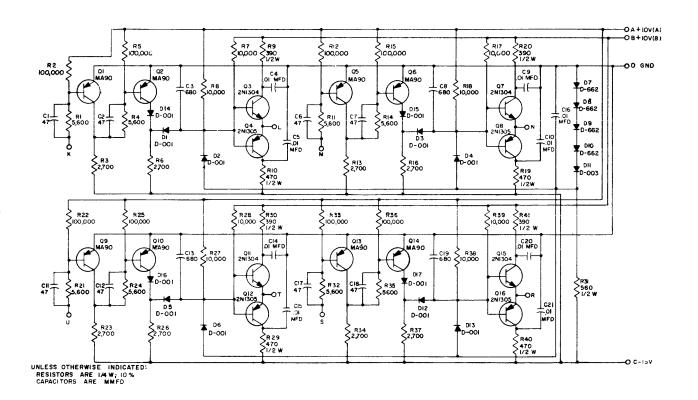

| BS-D-137-0-1          | Analog-to-Digital Converter                           | 10-109         |

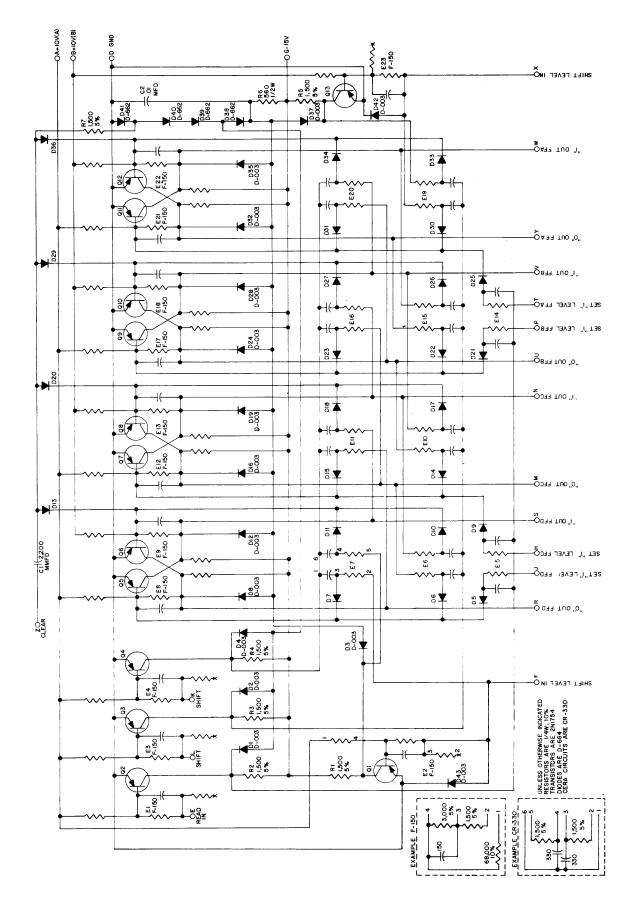

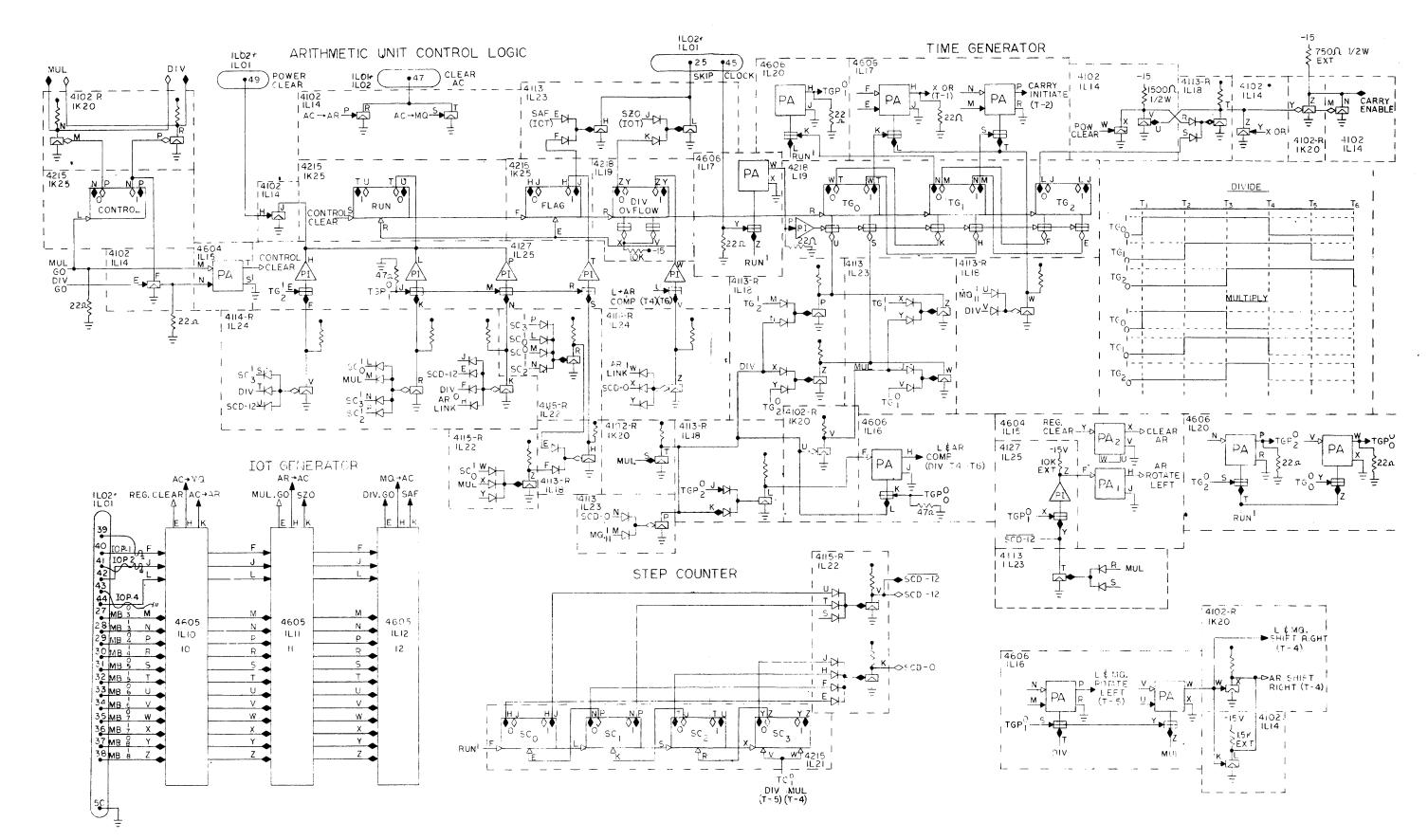

| BS-D-153-0-5          | AR Control, IOT Gen., Step Counter, Time Gen          | 10-111         |

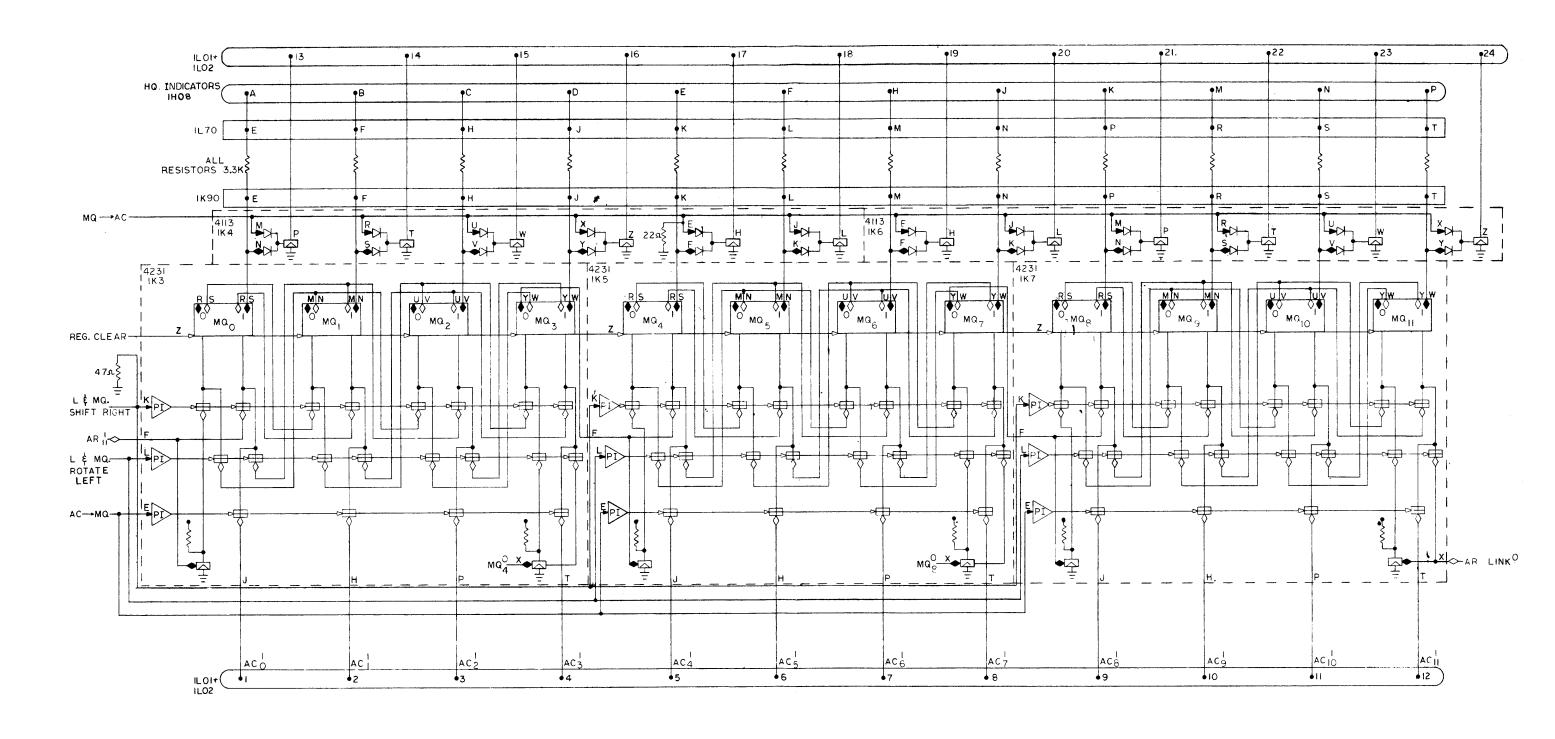

| BS-D-153-0-6          | MQ Register                                           | 10-113         |

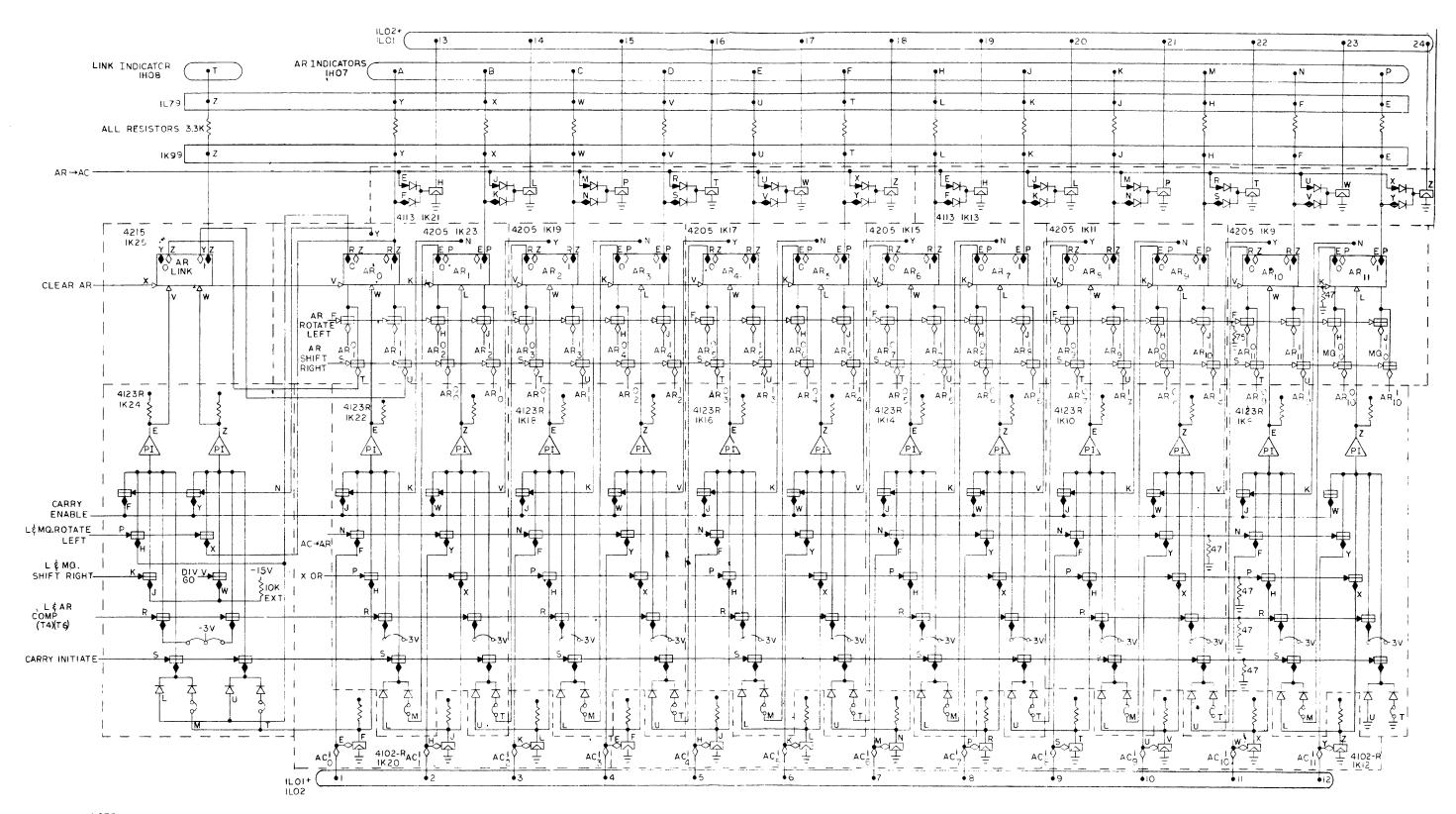

| BS-D-153-0-7          | AR Register                                           | 10-115         |

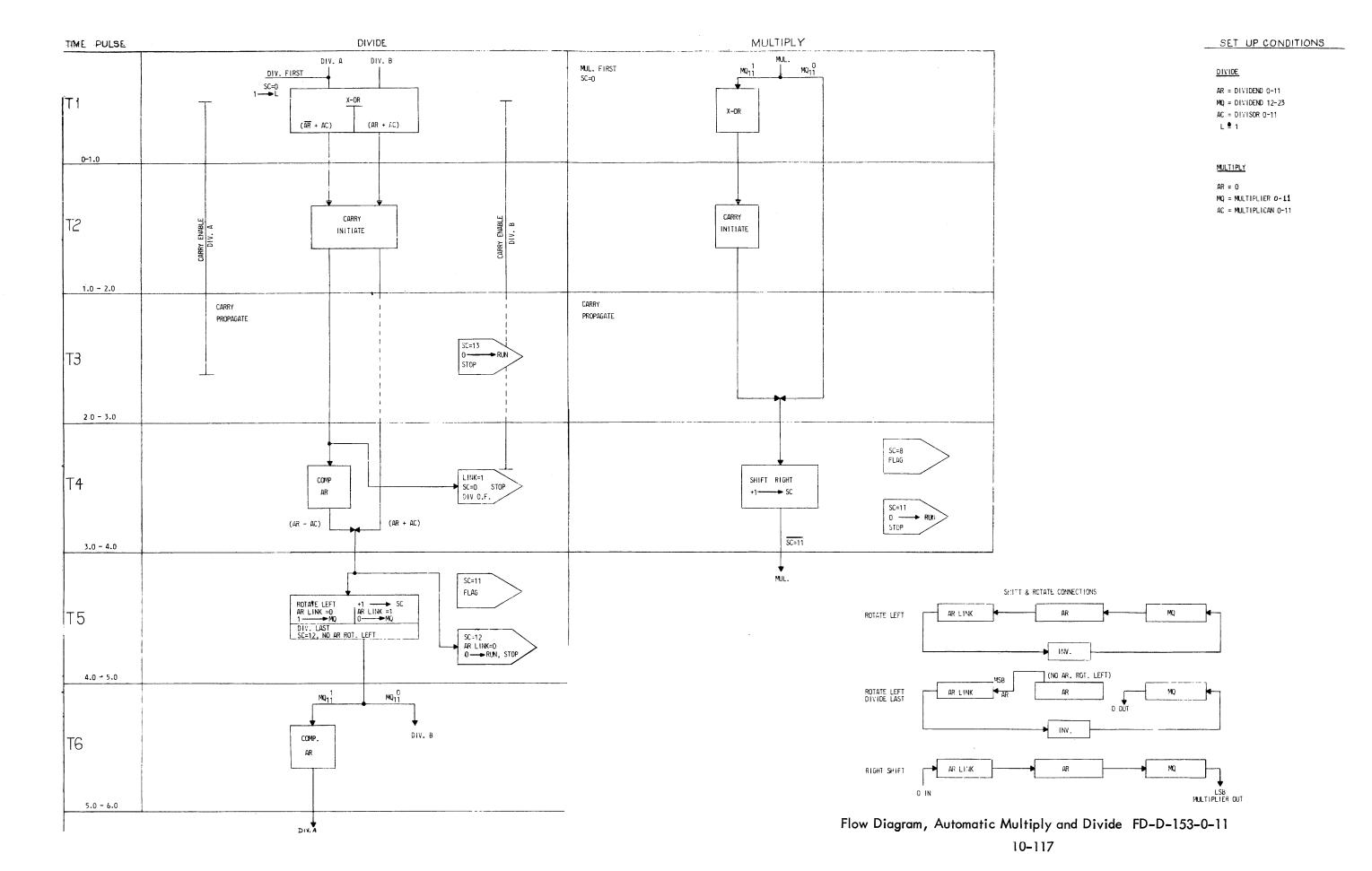

| FD-D-153-0-11         | Flow Diagram, Automatic Multiply and Divide           | 10-11 <i>7</i> |

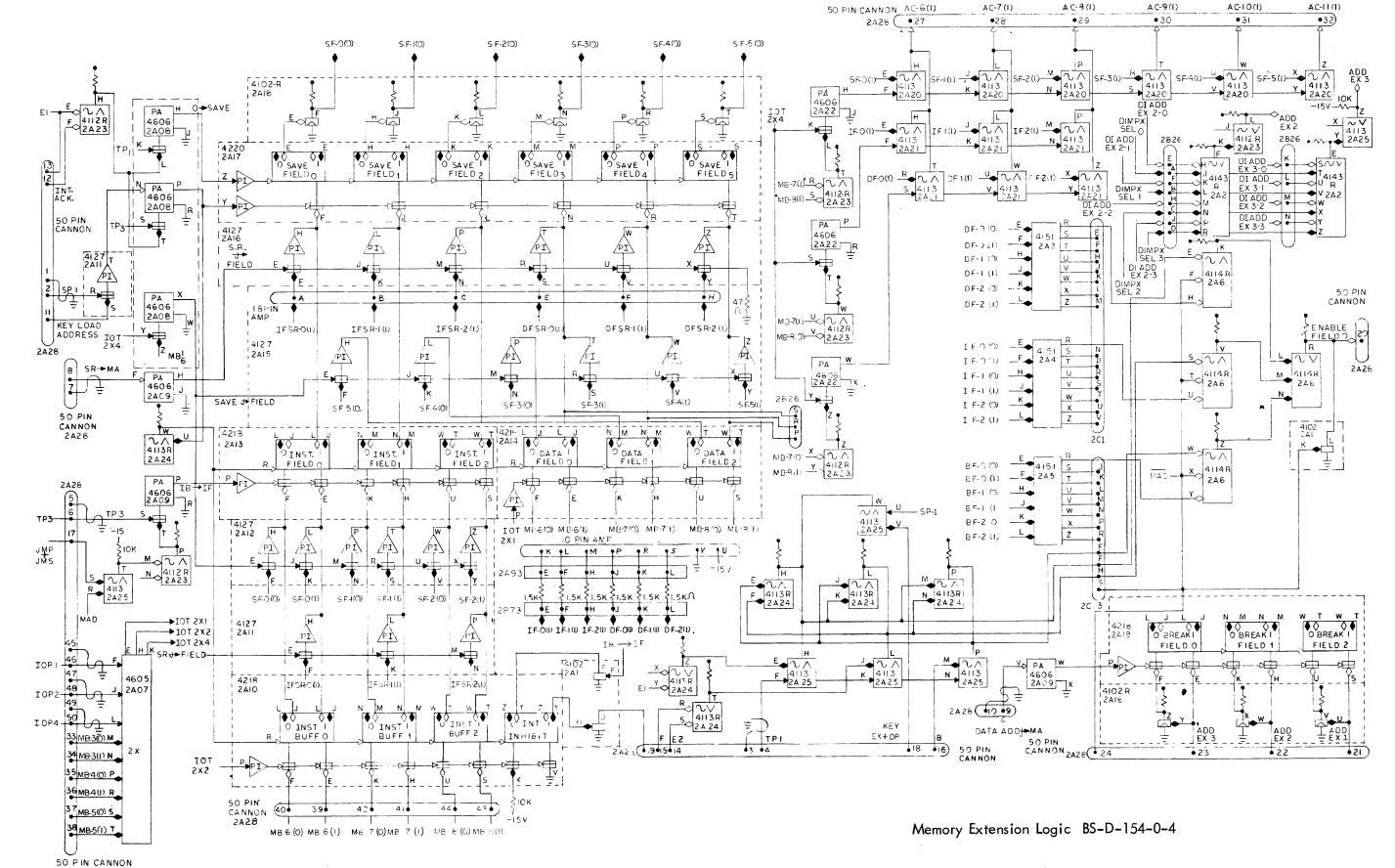

| BS-D-1 <i>5</i> 4-0-4 | Memory Extension Logic                                | 10-119         |

| ML-D-5-0-15           | System Module Location                                | 10-121         |

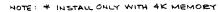

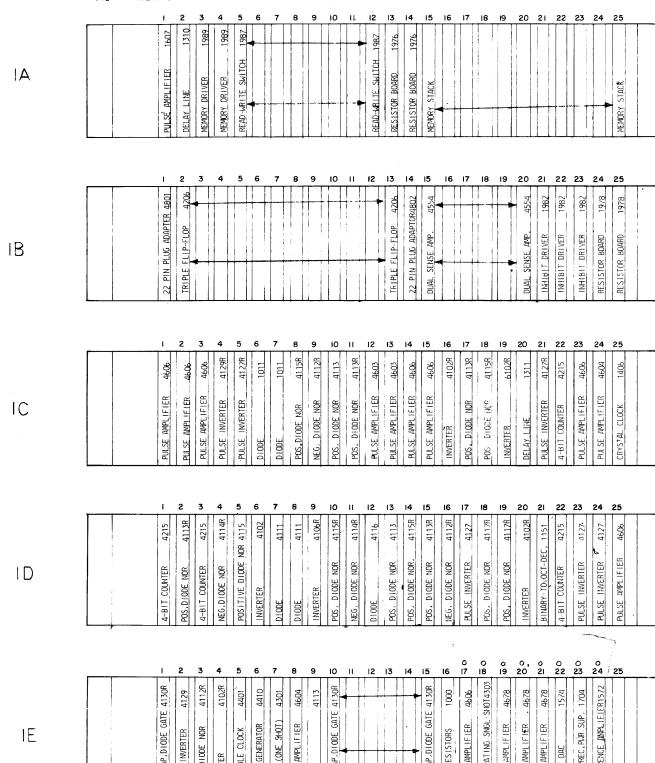

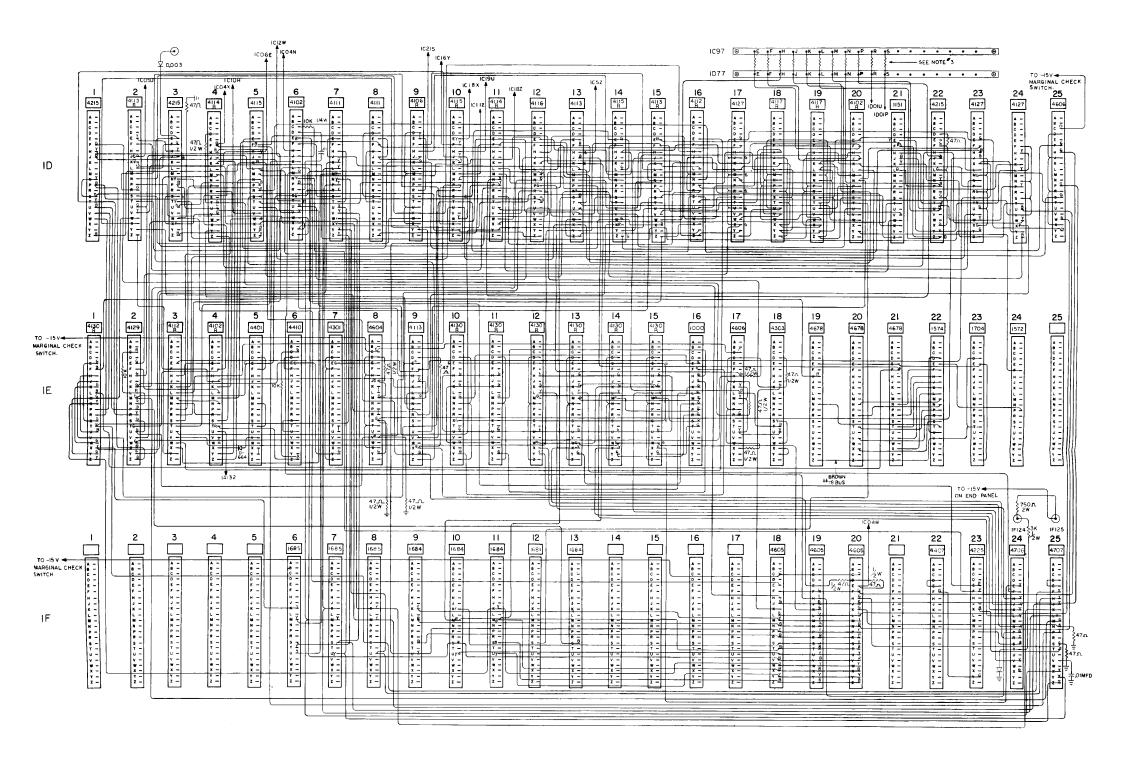

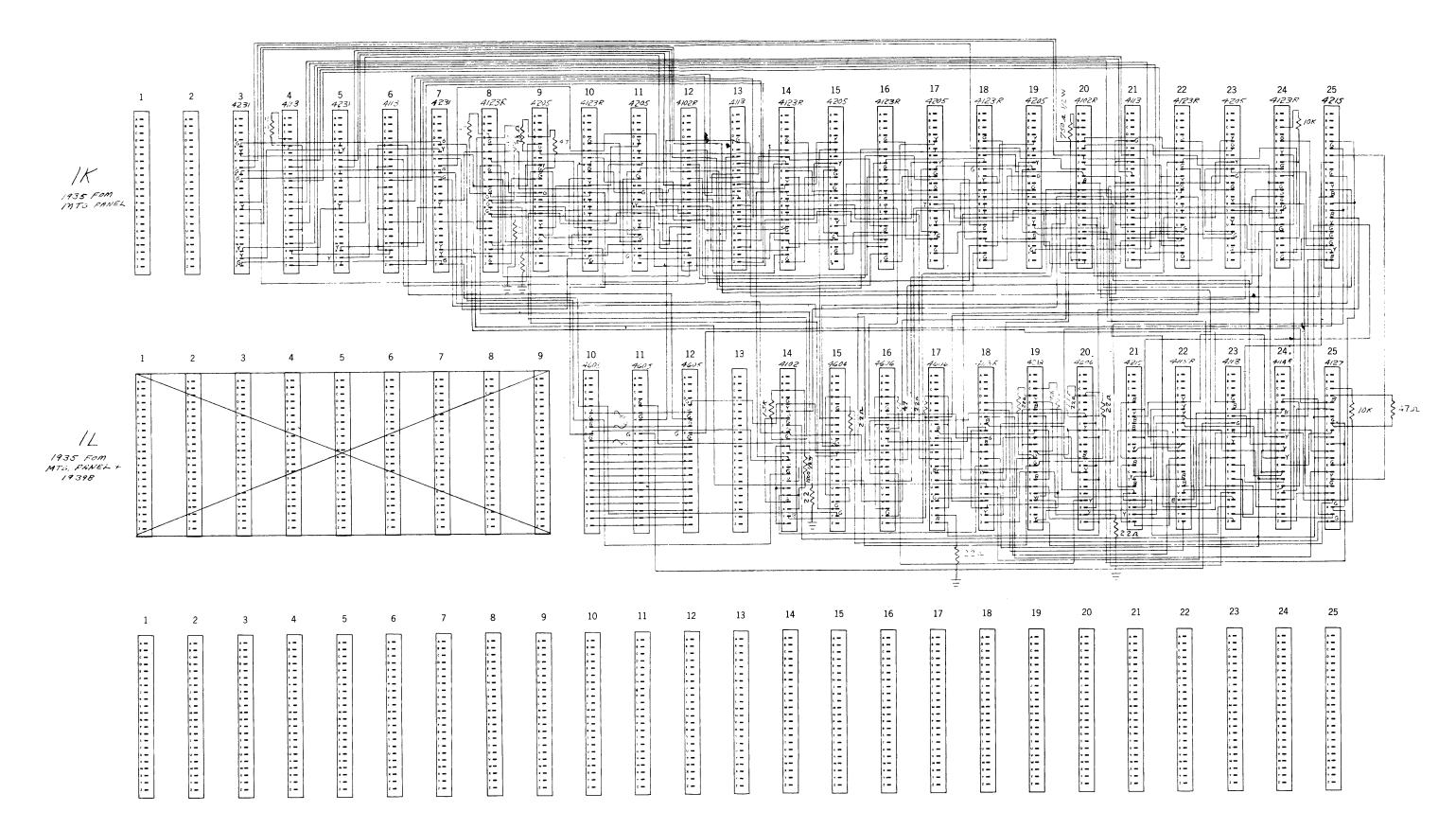

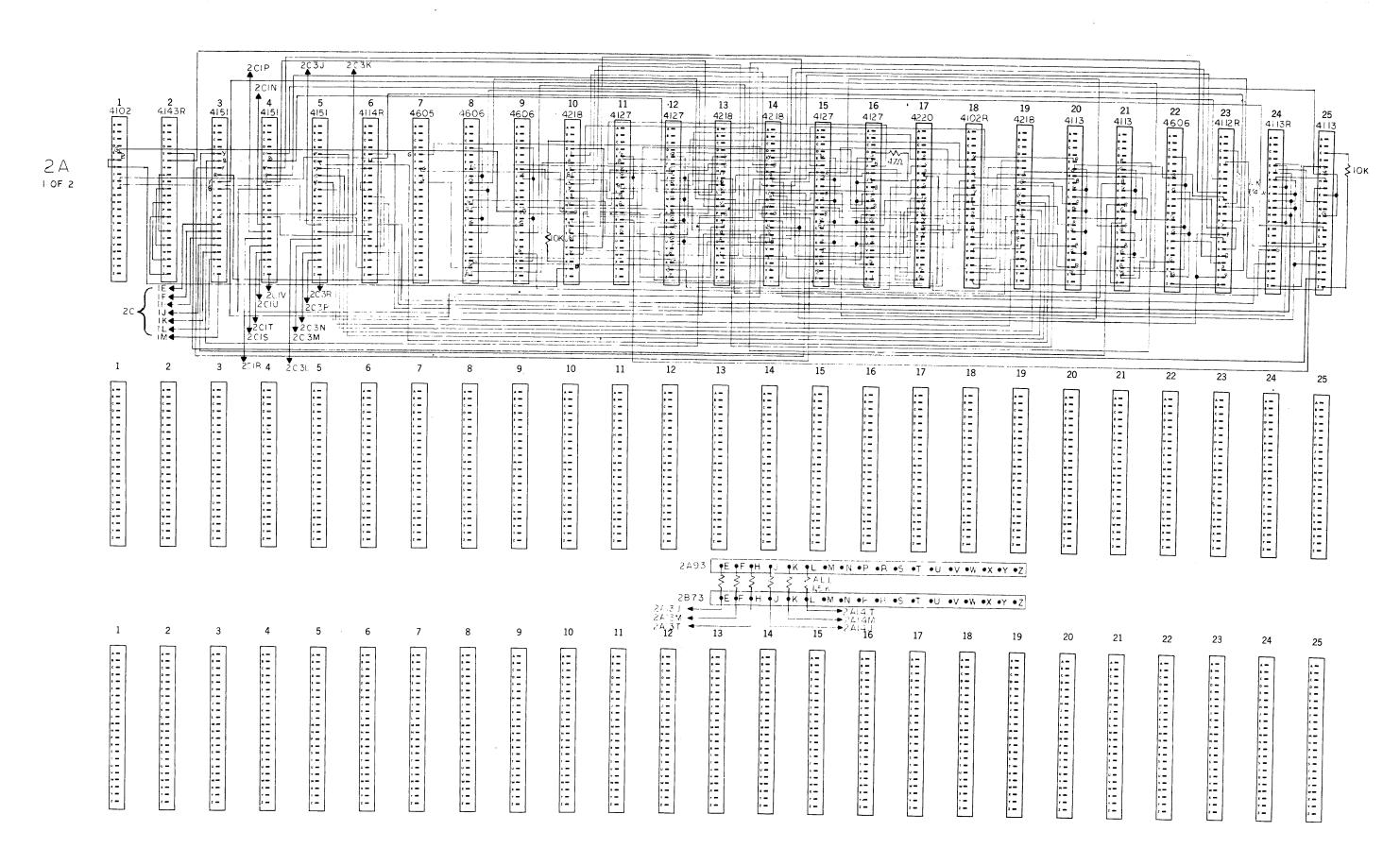

| WD-E-5-0-3            | Wiring Diagram 1A, 1B, 1C                             | 10-123         |

| WD-E-5-0-4            | Wiring Diagram 1D, 1E, 1F                             | 10-125         |

| WD-D-5-0-10           | Operator Control Keys and Switches                    | 10-127         |

| UML-D-153-0-3         | Utilization Module List for Type 153                  | 10-129         |

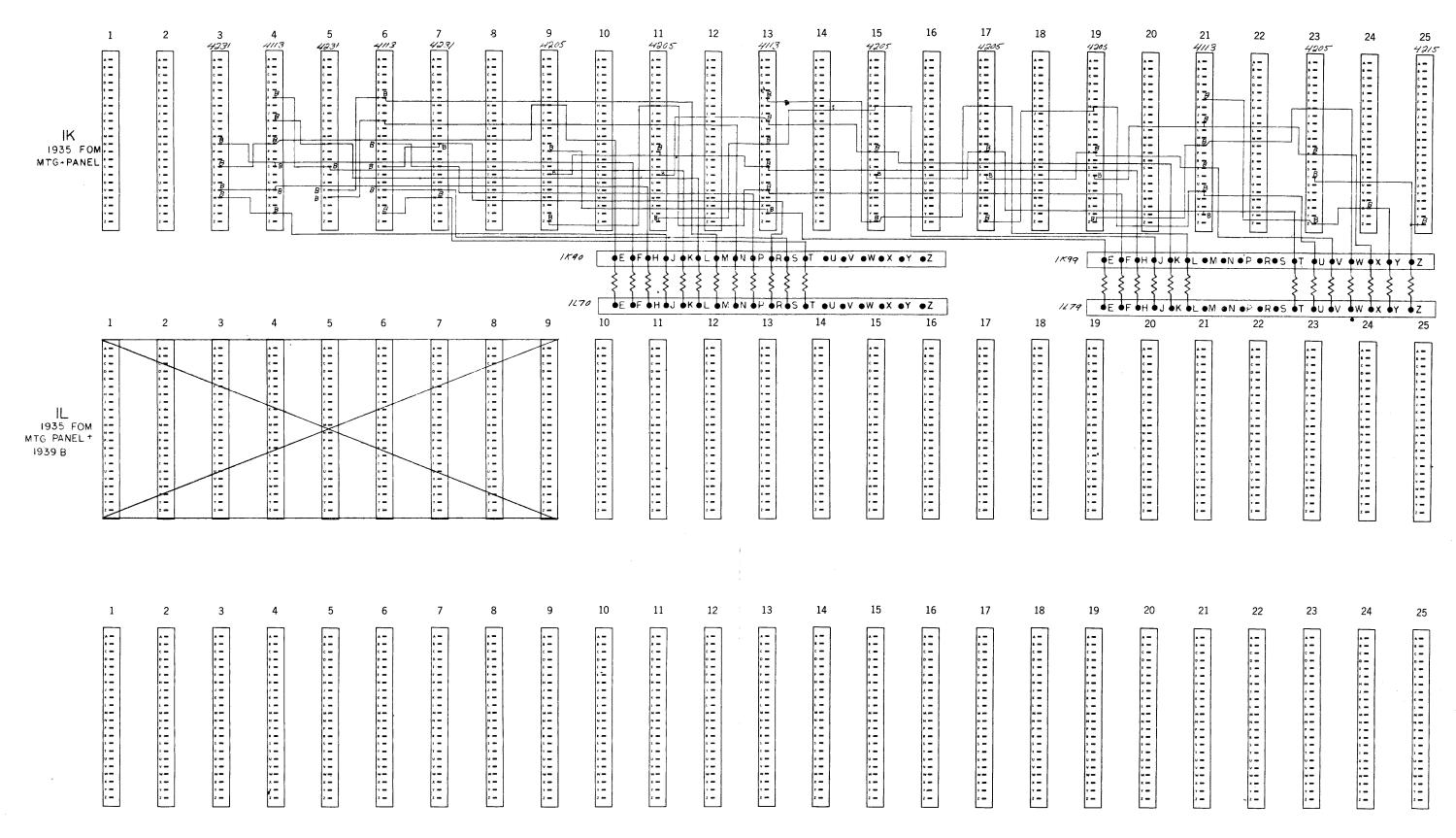

| WD-D-153-0-4          | Wiring Diagram 1K and 1L (Sheet 1 of 2)               | 10-131         |

| WD-D-153-0-4          | Wiring Diagram 1K and 1L (Sheet 2 of 2)               | 10-133         |

| UML-D-154-0-6         | Utilization Module List for Type 154                  | 10-135         |

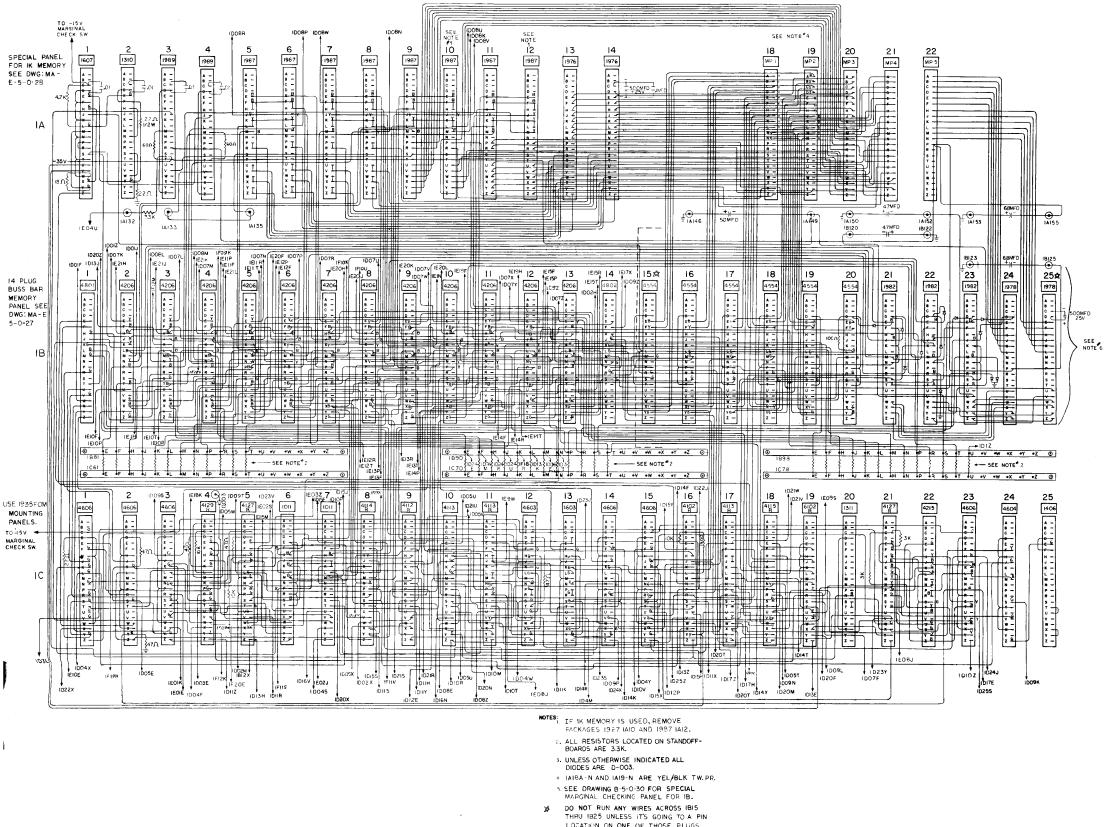

| WD-D-154-0-5          | Wiring Diagram for Type 154                           | 10-137         |

Figure 1-1 A Standard PDP-5 System

## SECTION 1

## INTRODUCTION AND DESCRIPTION

The Digital Equipment Corporation (DEC) Programmed Data Processor-5 (PDP-5) is a small, general-purpose, stored-program, digital computer that performs 2's complement binary arithmetic. The PDP-5 is a 1-address, 12-bit, parallel machine with a 6-microsecond cycle time. A standard PDP-5 contains a 1024- or 4096-word ferrite-core memory, which can be expanded in fields of 4096 words to a 32,768-word maximum by the addition of memory options. High-capacity, flexible, input/output circuits of the computer allow it to operate all types of modern peripheral data processing equipment and many types of process control instruments. Standard equipment for the PDP-5 includes a Teletype unit that provides an input to the computer from a keyboard or perforated tape and provides a page printer or perforated-tape output.

#### COMPUTER ORGANIZATION

The PDP-5 is a completely integrated system constructed of standard DEC system modules using transistor-diode switching circuits and self-contained solid-state power supplies. The computer operates on static dc levels, or the shift of them, and is organized into a data processor, a core memory, and facilities for input/output devices. The major functional elements of the PDP-5 and their signal interrelationship are shown in Figure 1-2.

#### **Processor**

All arithmetic, logic, and system control operations of the standard PDP-5 are performed by the processor. The major circuit elements which perform these functions are as follows:

Accumulator (AC) – The AC is the primary arithmetic register of the PDP-5. It also serves as an input/output register for programmed information transfers between core memory and peripheral equipment.

Link (L) - This 1-bit register serves as an extension of the AC and is used as a carry or over-flow register for arithmetic operations.

Figure 1-2 Simplified Block Diagram

Memory Buffer Register (MB) - The MB serves as a buffer register for all information passing between the processor and the core memory. The MB also serves as a buffer directly between core memory and peripheral equipment during data break information transfers and is used as a digital shift register for the Type 137 Analog-To-Digital Converter option.

Memory Address Register (MA) - The location in core memory which is selected for data storage or retrieval is determined by the MA. This 12-bit register can directly address all 4096 words of the standard core memory.

Instruction Register (IR) - This 4-bit register is loaded from the four most significant bits of the MB during a fetch cycle and so contains the four most significant bits of the instruction to be performed. The contents of the three most significant bits of the IR are decoded to produce the eight instruction performed by the computer. The least significant bit of the IR serves as a control bit to specify direct or indirect addressing of core memory to locate the operand during memory reference instructions, and is used to differentiate between the two groups of operate instructions.

Major State Generator - Two or more major control states are entered to determine and execute an instruction. The major state generator produces the signals which determine the machine state during each computer cycle. Each state is produced as a function of the current instruction, the current state, and the condition of the Break Request signal supplied to an input bus by peripheral equipment.

Program Counter (PC) - The address in core memory from which the next instruction will be drawn is controlled by the PC. The PC is located in address 0000 of core memory.

Input Mixer (IM) - The IM extends the input gating capability of the accumulator to allow it to handle information received from the switch register, the Teletype unit, and from peripheral equipment.

Switch Register (SR) – Twelve toggle switches on the operator console allow manual selection of addresses to be set into the MA and data to be written in core memory by passing through the IM, AC, and MB.

Output Bus Drivers - When necessary, output signals from the computer can be power amplified by removal of dummy plugs and insertion of output bus driver modules.

Basic Timing Generators – Timing pulses used to determine the 6-microsecond computer cycle time and produce time-synchronized gating operations are produced by the timing signal generator. Timing pulses used during operations resulting from use of the keys and switches on the operator console are produced by the special pulse generator. Pulses that reset registers and control circuits during power turn on and turn off operations are produced by the power clear pulse generator.

Control Elements – Circuits are also included in the PDP-5 that produce the IOP pulses that initiate operations involved in input/output transfers, determine the advance of the computer program under normal and I/O halt/restart conditions, allow instructions to be skipped as a function of the status of registers and control circuits within the computer or in peripheral equipment, and allow peripheral equipment to cause an interruption of the main computer program to transfer program control to a subroutine which performs some service for the I/O device. Other control elements generate the signals that control and activate the AC, MB, and MA.

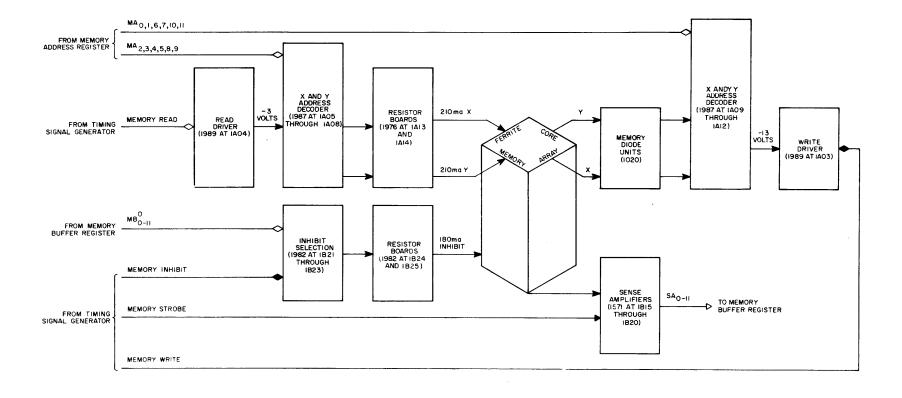

#### Core Memory

Permanent (longer than one instruction time) local information storage and retrieval operations are performed by the core memory. The memory is continuously cycling, automatically performing a read and write operation during each computer cycle. Input and output address and data buffering for the core memory is performed by the MA and MB of the processor, and operation of the memory is under control of signals produced by the timing signal generator of the processor. The major functional elements of the core memory are as follows:

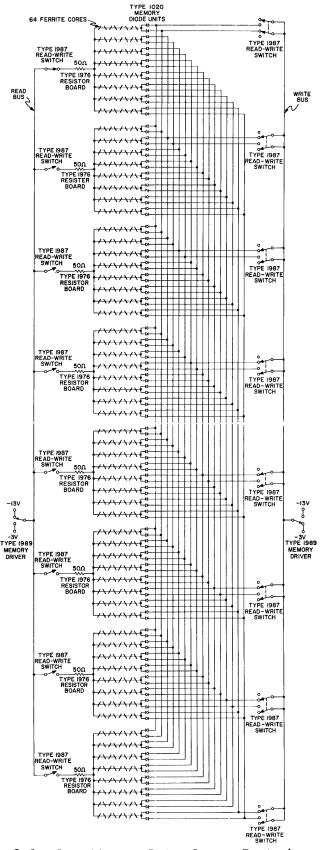

Memory Drivers - The direction of read-write drive current passing through the address drive lines of the core memory is determined by the memory drivers.

Address Selection - Addresses contained in the MA are decoded to enable passage of readwrite current through an X and a Y drive line of the core memory.

Inhibit Selection – Data to be written in core memory is contained in the MB. Since the read-write current passing through the address selection lines produce binary ones in each bit of the addressed memory register, the inhibit selection circuits inhibit setting of cores in planes corresponding to bits of the MB containing zeros.

Memory Diode Units and Core Array – The ferrite core array consists of 12 planes that are 64 cores wide by 64 cores deep for a 4096-word memory. Memory diode unit modules connected directly to the array prevent read-write current from passing through unselected drive lines.

Sense Amplifiers – Signals induced on the sense windings of the core array during reading are detected by the sense amplifiers and converted to pulses that set corresponding bits of the MB to transfer information from a specific address in core memory to the MB.

## Input/Output

Interface circuits for the processor allow bussed connections to a variety of peripheral equipment. Each input/output device is responsible for detecting its own select code and for providing any necessary input or output gating. Individually programmed data transfers between the processor and peripheral equipment take place through the accumulator. Single or multiple data transfers can be initiated by peripheral equipment, rather than by the program, by means of the data break facilities. Standard features of the PDP-5 also allow peripheral equipment to perform certain control functions such as program stop and start by means of the I/O halt and restart facilities, instruction skipping, and program control transfers initiated by a program interrupt.

Standard peripheral equipment provided with each PDP-5 system consists of a Teletype Model 33 Automatic Send Receive set and a Teletype control. The Teletype unit is a standard machine operating from serial 11-unit-code characters at a rate of ten characters per second. The Teletype provides a means of supplying data to the computer from perforated tape or by means of a keyboard, and supplies data as an output from the computer in the form of perforated tape or typed copy. The Teletype control serves as a serial-to-parallel converter for Teletype inputs to the computer and serves as a parallel-to-serial converter for computer output signals to the Teletype unit.

Facilities for the Type 137 Analog-To-Digital Converter are wired into each PDP-5. The converter operates by the successive approximation process, using the computer memory buffer register as a distributor shift register and using the accumulator as a digital buffer register. Conversion time for this option is a function of the predetermined accuracy, which varies

from 24.5 microseconds for 6-bit accuracy to 132 microseconds for 11-bit accuracy. The converter is able to use the registers of the computer because it stops the computer program by means of the I/O halt facility during its operation. Space and wiring within the processor are provided so that activation of this option requires little more than insertion of eight modules in a mounting panel.

Standard equipment, which can be obtained as peripheral equipment for the PDP-5 at the customer's option, includes high-speed perforated-tape readers and punches, card readers and punches, line printers and digital plotters, a variety of cathode-ray tube display equipment, a choice of magnetic tape equipment, Teletype data communication equipment, and multiplexer equipment which allows up to four I/O devices to use the computer data break facilities.

## FUNCTIONAL DESCRIPTION

Operation of the computer is accomplished on a limited scale by keys on the operator console. Operation in this manner is limited to address and data storage by means of the switch register, core memory data examination, the normal start/stop/continue control, and the single step or single instruction operation that allows a program to be monitored visually as a maintenance operation. Most of these manually initiated operations are performed by executing an instruction in the same manner as by automatic programming, except that the gating is performed by special pulses rather than by the normal clock pulses. In automatic operation, instructions stored in core memory are loaded into the MB and executed during two or more computer cycles. Each instruction determines the major control states that must be entered for its execution. Each control state lasts for one 6-microsecond computer cycle and is divided into six 1-microsecond time states which can be used to perform logical operations. Performance of any function of the computer is controlled by gating of a specific instruction during a specific major control state and a specific time state.

#### Instructions

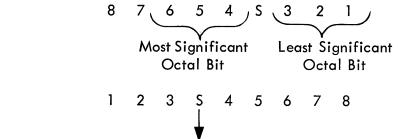

The three most significant bits of words brought from core memory which are to be used as instructions are loaded into the IR. The IR decodes the first three bits as the operation code to generate the eight instruction signals. Instructions that store or retrieve data from core memory are called memory reference instructions and are designated by operation codes 0 through

5. Instructions that do not reference core memory can be microprogrammed to cause a variety of operations to be performed as a function of binary ones in the remaining nine bits of the instruction. In a sense, these instructions use bits 3 through 11 to augment (or as an extension of) the operation code. Augmented instructions with an operation code of 6 perform input/output transfer (IOT) operations, and instructions with an operation code of 7 perform local data handling and control operations (OPR). Microprogramming of the IOT instruction allows combining of several bits to perform multiple operations within the limit of the capabilities of the peripheral equipment selected. Microprogramming of the operate instruction allows bit combinations and multifunction operations to be performed in two groups, as determined by the contents of bit 3 of the instruction. The format of all instruction classes is indicated in Figure 1-3.

Figure 1-3 Instruction Formats

A memory reference instruction specifies a 12-bit core memory address for the operand in one of the following four ways:

a. When bits 3 and 4 of the instruction contain zeros, bits 0 through 4 of the address are zeros and bits 5 through 11 of the address are taken from the corresponding bits of the instruction.

- b. When bit 3 contains a 0 and bit 4 contains a 1, bits 0 through 4 of the address are the same as the address of the current instruction and bits 5 through 11 are taken from corresponding bits of the instruction.

- c. When bit 3 contains a 1 and bit 4 contains a 0, the address of the operand is taken from the content of the core memory register whose address contains zeros in bits 0 through 4 and corresponds to the content of the instruction for bits 5 through 11.

- d. When both bits 3 and 4 contain ones, the address of the operand is taken from the content of the core memory register at an address corresponding to the address of the current instruction for bits 0 through 4 and corresponding to the content of the current instruction for bits 5 through 11.

The memory reference instructions are as follows:

AND (operation code 0) - The logical AND. This operation is performed between the content of the specified core memory register and the content of the accumulator. The result of this combination is left in the accumulator; the original content of the accumulator is lost, and the content of the addressed core memory register is restored.

TAD (operation code 1) - Twos complement add. The content of the specified core memory address is added to the content of the accumulator in 2's complement arithmetic. The result is left in the accumulator, the original content of the accumulator is lost, and the content of the addressed core memory register is restored. If there is a carry from AC<sub>0</sub> during this operation, the link is complemented.

ISZ (operation code 2) - Index and skip if zero. The content of the specified core memory register is incremented by one in 2's complement arithmetic and then restored. If the result of this incrementing is zero, the program counter is incremented an additional time so that the succeeding instruction is skipped.

DCA (operation code 3) - Deposit and clear accumulator. The content of the AC is deposited in the core memory location specified, and the content of the accumulator is cleared. The previous content of the specified core memory register is lost.

JMS (operation code 4) - Jump to subroutine. The content of the program counter is incremented by one and depositied at the specified core memory location. The next instruction is taken from the content of the specified core memory address +1.

JMP (operation code 5) - Jump. The core memory address specified in the instruction is set into the program counter so that the next instruction is taken from this specified core memory address. The original content of the program counter is lost.

An augmented instruction having an operation code of 6 is designated an input/output transfer (IOT) instruction and uses bits 3 through 8 to signify a select code for a specific I/O device or register, enabling it to produce IOT pulses during computer time states T4, T5, and T6 as a result of binary ones in bits 11, 10, and 9 respectively of the instruction. These IOT pulses initiate operation of logic elements within the peripheral equipment and/or execute data transfers to or from the processor.

Augmented instructions having an operation code of 7 specify the operate (OPR) instruction. When bit 3 of an OPR instruction contains a 0, a group 1 (OPR1) microinstruction is indicated; and when bit 3 contains a 1, a group 2 (OPR2) microinstruction is indicated. Group 1 microinstructions are used primarily for clearing, complementing, rotating, and incrementing operations, and group 2 microinstructions are used principally in test and skip operations. Any logical combination of bits within one group can be combined into one microinstruction. Naturally, bits which cause diverse functions cannot be programmed simultaneously.

## Major States

Two or more states are entered during each instruction. Assuming that the core memory address of the next instruction to be performed is contained in the MA, each instruction can be considered as beginning in the fetch state. The fetch state draws an instruction from core memory and begins executing it. At the conclusion of a fetch state other states are entered as a function of the current instruction. If no other states need be entered, the program count state is entered to load the content of the program counter into the MB, to modify the program count suitably, then to load the program count into the MA and the PC. At the conclusion of a program count state the fetch state is always entered. The operations performed in each of the major states are as follows:

Fetch (F) - During this state, instructions are brought from core memory and their operation code is transferred into the IR. The JMP, IOT, and OPR instructions are completely executed during the F state.

Execute 1 (E1) - The content of a core memory address specified by a memory reference instruction is loaded into the MB, and the instruction is executed during this state.

Execute 2 (E2) - This state is entered during a JMS instruction to write the program count into the core memory address specified by the instruction.

Defer (D) - The effective address of an indirectly addressed instruction is brought from core memory into the MB during this state.

Break (B) - This state is entered in response to a break request signal received from peripheral equipment and is used to execute data transfers directly between the MB and the device. Successive break cycles can be entered for multiple-word transfers. When the transfer has been completed, the normal program sequence is resumed.

Program Count (P) - This state is responsible for retrieving the program count from the PC at core memory address 0000 and modifying it according to the current instruction. Modification of the program count involves incrementing by one for non-branching instructions, incrementing by two for satisfied skip instructions, and changing the address for JMP or JMS instructions.

#### Time States

Six 1-microsecond time states designated T1 through T6 occur during each computer cycle (or major state). Major states are changed at the beginning of time state T6 of each cycle so that logical operations in the new major state can commence with time pulses produced during time state T1. Time pulses, designated TP, occur at the start of each time state except T2. These time pulses initiate gating circuits to perform sequential or synchronized logical operations. Core memory is automatically cycled during each computer cycle so that reading occurs during time states T2 and T3, and writing occurs during time states T5 and T6.

#### PHYSICAL DESCRIPTION

The standard PDP-5 is contained in a single DEC computer cabinet 60-1/8 inches high, 47 inches wide, and 27-1/16 inches deep. A table 30 inches wide and 18 inches deep is attached to the front of the cabinet, just below the operator console. The operator console contains all keys, switches, and indicators used in normal operation of the computer. When sufficient optional equipment is used with the standard PDP-5, additional cabinets are bolted to the main cabinet. In such cases, the table extends the width of two or more cabinets.

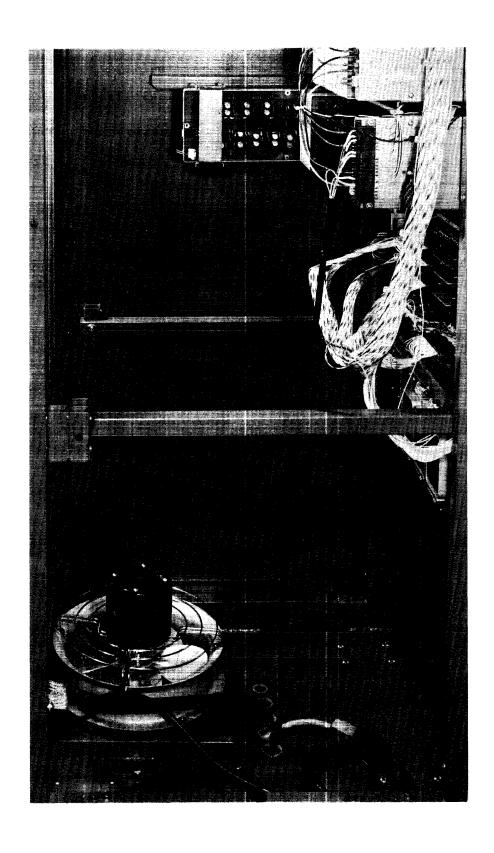

A cabinet is constructed of a welded steel frame covered with sheet steel. Double rear doors are held closed by magnetic latches. A full-width plenum door provides mounting for the power control and power supplies inside the double doors. Controls and indicators used in maintenance activities are located on components mounted on the plenum door. The plenum door is latched by a spring-loaded pin at the top. Double doors at the front of the cabinet conceal module mounting panels above and below the operator console. These mounting panels are positioned within the cabinets so that the connector block wiring is accessible by opening the front doors, and the modules are accessible from the back of the equipment. A fan mounted in the bottom of each cabinet draws cooling air through a dust filter, passes it over the electronic components, and exhausts it through louvered panels and other openings in the cabinet. Four casters allow mobility of each cabinet.

A coordinate system is used to locate cabinets, module mounting panels, modules and signal cable connectors and terminals within a PDP-5 system. The cabinet containing the operator console is always designated cabinet 1, and additional cabinets may be numbered from left to right or right to left, depending upon the configuration. Each 5-1/4 inch position on the front of a cabinet is assigned a capital letter, beginning with A at the top. Figure 1-4 indicates the location of components within the standard PDP-5. Modules are numbered from 1 through 25 from left to right in a mounting panel, as viewed from the wiring side. Connectors on the connector panel (1J) are numbered from 1 through 6, from right to left as viewed from the back of the machine. Blank module and connector locations are numbered. Terminals on a module connector are designated by capital letters from top to bottom. The letters G, I, O, and Q are omitted from module and terminal designations. Therefore, 1C06Jis in cabinet 1(1), the third component location from the top (C), the sixth module from the left (06), and the ninth terminal from the top of the module (J). Components mounted on the plenum door are not identified by location.

Figure 1-4 Component Locations

The Teletype unit which is standard equipment with the PDP-5 can be used on either side of cabinet 1. This unit is approximately 33 inches high, 22-1/4 inches wide, and 18-1/2 inches deep and is described in detail in the Teletype technical manual.

## **SPECIFICATIONS**

| Physical        |                                                                                             |  |

|-----------------|---------------------------------------------------------------------------------------------|--|

| Cabinet Height: | 69-1/8 inches                                                                               |  |

| Cabinet Width:  | 22-1/4 inches for a single-cabinet PDP-5 (30-inch table) 42 inches for a dual-cabinet PDP-5 |  |

| Cabinet Depth:  | 45-1/16 inches                                                                              |  |

Cabinet Door Clearance:

14-7/8 inches at back

Teltype Height:

33 inches to top of console

44-1/4 inches to top of copyholder

Teletype Width:

22-1/4 inches

Teletype Depth:

18-1/2 inches

Cabinet Weight:

540 pounds for a standard PDP-5

890 pounds (average) for a dual-cabinet PDP-5

Teletype Weight:

40 pounds

Electrical

Power Requirements:

115 volts, 60 cycles, 1 phase, 7.5 amperes

for standard PDP-5 (can be constructed for

220 volts or 50 cycles upon special request)

Power Dissipation:

780 watts

Digital Signal Levels:

ground and -3 volts

Ambient Conditions

Operating Temperature:

50 to 104°F (10 to 40°C)

Operating Humidity:

0 to 90% relative humidity

Storage Temperature:

32 to 104°F (0 to 40°C)

Storage Humidity:

less than 90%

Heat Dissipation:

2370 BTU/hour

Functional

Cycle Time:

6 µsec

Word Length:

12 bits

Core Memory Size:

1024 or 4096 words, expandable to 32,768

in fields of 4096 words.

Instructions:

8 basic instructions, 6 memory reference and 2 augmented. The augmented instructions are microprogrammed to pro-

duce more than 100 commands.

Input/Ouput Capability:

64 different devices can be individually selected and addressed by 3 command pulses.

#### SYMBOLS AND TERMINOLOGY

Engineering drawing numbers for this equipment contain five pieces of information, separated by hyphens. Read from left to right these bits of information are a lettered code specifying the type of drawing, a lettered code specifying the size of the drawing, the type number of the equipment, the manufacturing series of the equipment, and the number of a drawing within a particular series. The drawing type codes are:

- a. BS, block schematic or logic diagram

- b. CL, cable list

- c. FD, flow diagram

- d. ML, module location diagram

- e. RS, replacement schematic

- f. UML, utilization module list

- g. WD, wiring diagram

In the succeeding sections of this manual, block schematic engineering drawings are specified only by the drawing number. A reference to engineering drawing 9 is interpreted as a reference to BS-E-5-0-9. Block schematic drawings for optional equipment and for all other type drawings are referenced by the complete identification number.

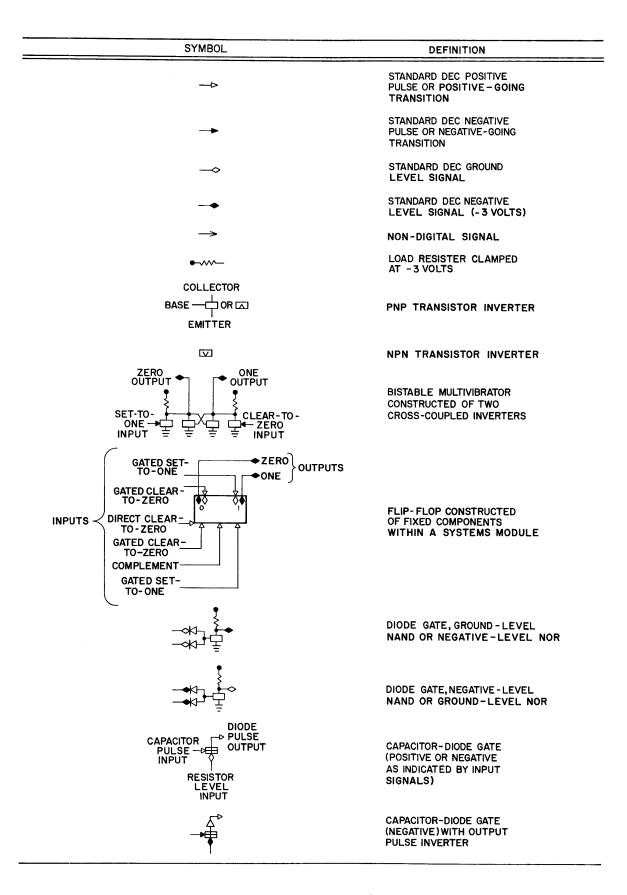

Symbols used on engineering drawings to represent basic logic circuits are defined in Figure 1-5.

Figure 1-5 Logic Symbols

Conventions and notation on engineering drawings and in text describing the PDP-5 are used as follows:

| ٧                      | Programming notation for the inclusive OR function.                                                                   |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| <b>+</b>               | Programming notation for the exclusive OR function.                                                                   |

| ٨                      | Programming notation for the AND function.                                                                            |

| =>                     | Programming notation for an information transfer.                                                                     |

| +                      | Design notation for the inclusive OR function and program notation for addition.                                      |

|                        | Design notation for the AND function.                                                                                 |

|                        | Design notation for an information trans-<br>fer accomplished by a single signal (used<br>without parentheses).       |

| <del>-J</del> ▶        | Design notation for a jam transfer of information accomplished by gating both the 1 and 0 inputs of a storage device. |

| ()                     | The content of a storage device.                                                                                      |

| $C(A) \lor C(B) =>(A)$ | The content of register B is OR com-                                                                                  |

The contents of bits 0 through 5 of register A are jam transferred into the contents of bits 6 through 11 of register B.

All Bit 2 of register A is in the state corresponding to a binary 1, or contains a 1.

A2(1) Same as above.

The content of A is incremented by 1.

Register A is cleared or set to contain

Other terms used in this manual are defined as follows:

set - means to set a storage device to the state corresponding to a binary 1.

all zeros.

clear - means to establish the state corresponding to a binary 0.

flag - a flip-flop or signal that is sensed by the program to indicate a specific equipment condition or status.

instruction - a computer word which causes a specific machine function and which is identified by a distinct operation code.

microinstruction – an instruction in which numerous different machine functions can be programmed by the placement of ones and zeros in bits other than in the operation code. Effectively the entire word is used as an operation code which is decoded, not only by the instruction register, but by gating circuits within the machine.

command – a signal that causes a specific operation to occur as the whole or partial execution of an instruction or microinstruction.

subroutine - a routine that can be called upon from any core memory address of the main program to provide a service to the main program or peripheral equipment, usually to perform operations that are repeated many times, and thus to simplify the main program.

program interrupt – an interruption in the main program caused by transfer of program control to a subroutine, after storing the current program count. The interruption is initiated by peripheral equipment to cause a subroutine to be executed. Usually the subroutine is used to locate the equipment that caused the interrupt and to transfer information with it, or service it in some way.

data break - a temporary halt or break in the main program used to transfer data with peripheral equipment under control of the peripheral equipment (not under direct computer program control).

operand - a stored number to be mathematically operated upon.

address of the operand - the location of a core memory register currently containing the operand.

absolute address - a 12-bit number used directly to specify any address in core memory.

effective address - the address of the operand as specified in an instruction or by an absolute address.

#### SECTION 2

#### **PROCESSOR**

The major arithmetic, logic, and control functions performed by the PDP-5 are accomplished by logic circuit elements of the processor. All operations of the PDP-5 are performed by the processor except those directly concerning data storage and retrieval in core memory, and information transfers to or from peripheral equipment. In performing these operations the processor draws instructions from core memory and executes them by sequentially entering one of six major control states. Each control state lasts for the duration of one computer cycle in which there are six time states, each of which produces various logical operations depending upon the major control state.

Functional operation of the processor can be compared to a three dimensional matrix. As in the matrix an X, Y, and Z coordinate must be specified to locate a given point, so within the processor an instruction, major state, and timing pulse determine the specific logic function performed. A change in any of these three items changes the resultant logical operation. Therefore, assuming one instruction and one state, as many different operations may be executed as there are timing pulses employed. In general, states are entered as a function of the current instruction, except that the break state is initiated by a break request originating in peripheral equipment, and the program count state is entered to locate the next instruction when no other state need be entered. Execution of each of the eight instructions requires two or more states to be entered. Each state lasts for 6 microseconds and so has five timing pulses available for initiating sequential logical operations.

## POWER CLEAR GENERATOR (5)

During the power turn on sequence, the power clear generator produces repeated Power Clear pulses at a 500 kc rate. These pulses clear the run and I/O-hlt flip-flops to assure that transients within the machine do not start computer operation. These pulses are also supplied to terminals 1J01-49 and 1J03-47 of the interface connectors and to the line unit out (LUO) buffer of the Teletype control to assure that registers of I/O devices are cleared or are in some preset state prior to programmed operation. The logic circuits for this functional element are shown on the upper left side of engineering drawing 5.

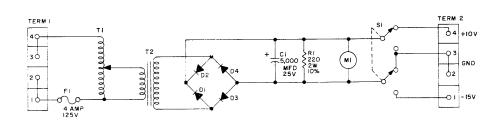

In the power turn on sequence, the 735 Power Supply, which produces the memory currents, is energized through the delayed closure/fast release contact K2 of the 832 Power Control. The time delay of K2 is between 3 and 5 seconds, so for this period of the turn on sequence the -35 volt output of the 735 supply is essentially at ground potential. The ground potential is supplied through the centertap of the power transformer and diode D4 of the rectifier in the 735 Power Supply. This potential from terminal E of the 735 Power Supply is isolated by two series-connected inverters of the 4102 module at location 1E04 and is used to enable or disable the 4401 Clock module at location 1E05. The initial ground potential is isolated from the clock module by an external diode connected to terminal V, so the clock is uninhibited and generates the standard DEC negative pulses designated the Power Clear pulses. After the initial delay the -35 volt power supply output causes a -3 volt level to be supplied to terminal V of the clock from the clamped load resistor of the last inverter. This level inhibits operation of the clock and prevents generation of Power Clear pulses during full computer excitation.

## SPECIAL PULSE GENERATOR (5)

Operation of the keys and switches causes the computer to perform functions similar to those performed automatically during execution of instructions. These operations require sequenced timing pulses which are provided by the special pulse generator. The special pulse generator is shown on the upper left portion of engineering drawing 5.

Initiation of the special pulse generator occurs at the positive-going leading edge of the Key Manual signal. This signal is produced when any of the manual keys, except the STOP key, are operated. The Key Manual signal is inverted to produce the negative shift required to initiate operation of the 4410 Pulse Generator module at location 1E06. The output of this pulse generator is a 1-microsecond negative pulse, designated the SPO pulse, which is distributed to the run control element to clear the run flip-flop, to terminal 46 of interface connector 1J03, and to the pulse input of the 4301 Delay module at location 1E07. The delay module produces a 10-microsecond delay between generation of the SPO pulse, which is generally used to clear registers and control devices in peripheral equipment using the data break facility, and generation of the SP1 through SP3 pulses, which strobe registers or transfer information. The standard DEC negative pulse output of the delay module initiates operation of the first pulse amplifier circuit on the 4604 module at location 1E08. Each of the three pulse amplifier circuits on this

module produces a 1-microsecond negative pulse which is designated by an appropriate SP number. The series connection of these pulse amplifiers causes turn off of SP1 to initiate generation of SP2, and the turn off of SP2 to initiate generation of SP3. When SP3 expires, the special pulse generator has completed its operation and awaits another Key Manual signal, since this circuit is not regenerative.

### TIMING SIGNAL GENERATOR (17)

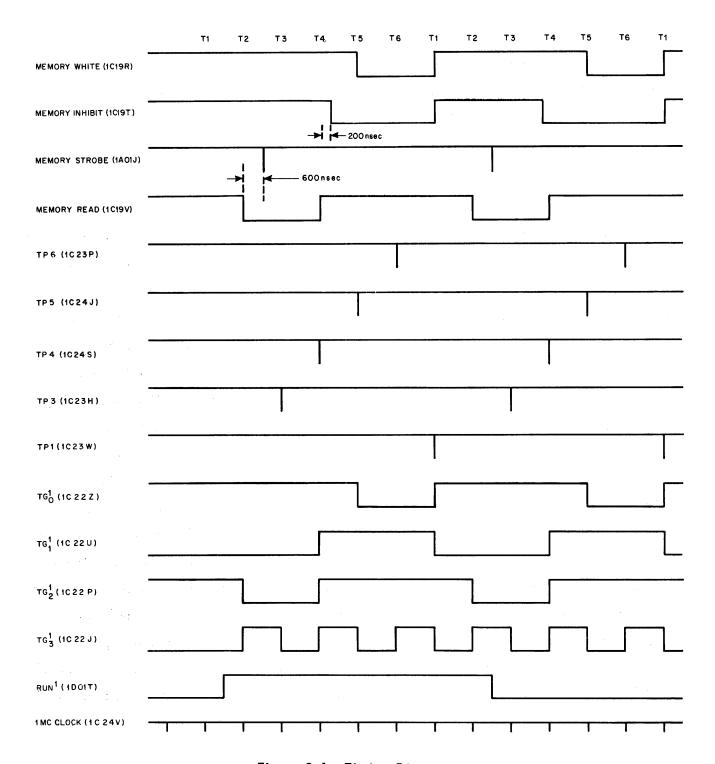

The basic timing cycle of the PDP-5 is determined by the 1406 Crystal Clock module at location 1C25. The standard DEC 70-nanosecond negative pulse output of this 1-megacycle crystal clock is converted to 400-nanosecond DEC standard negative pulses, required to operate the 4000 series system modules of the computer, by the 4604 Pulse Amplifier module at location 1C24. The negative pulse output from this pulse amplifier is supplied to terminal 45 of interface connector 1J01 and provides the trigger pulse input to the 4127 Pulse Inverter module at location 1C21 which drives the 4215 Four-Bit Counter module at location 1C22. All timing pulses used in automatic operation of the computer are derived from the state of these flipflops and are shown in the timing diagram of Figure 2-1. The pulse inverter circuit which drives the least significant bit  $(TG_3)$  of the counter is controlled by the 4115 Positive Diode NOR module at location 1D10 which functions as a ground-level NOR to enable the pulse inverter, and serves as a negative NAND gate to inhibit operation of the counter. Therefore, if any of the flip-flops in this 4-bit ring counter are in the 1 state except TG3, or if the run flip-flop is in the 1 status, a ground potential is applied to one of the signal inputs to this gate, and the counter is enabled and allowed to advance upon receipt of each output pulse of the crystal clock. Conversely, the counter will run until all inputs to this gate are negative; this occurs in time state T1 when the run flip-flop is in the 0 state. The state and/or transition of the 4-bit counter initiates operation of the 4604 and 4606 Pulse Amplifier modules at locations 1C24 and 1C23 to produce the TP pulses used throughout the logic circuits to initiate clockbased sequence operations.

When the computer is energized initially, the counter commences in time state T1, and so no TP1 pulse is generated as a function of the counter. A TP1 pulse is generated under either of the following conditions:

Figure 2-1 Timing Diagram

- During SP1 after operation of the CONTINUE key.

- b. When TG<sub>1</sub> changes from the 1 to the 0 state and either the EXAMINE or DEPOSIT key is operated, or the run flip-flop is in the 1 state, or the I/O-hlt flip-flop is in the 1 state.

This gating is effected by the negative NAND circuit of the 4113 module at location 1C11 and the ground-level NOR gate of the 4115 module at location 1D10 which provide enabling levels to the pulse amplifier circuit producing the TP1 pulse. Therefore, the TP1 pulse is produced for each machine cycle except the first cycle of operation initiated by the START key, and during time state T1 immediately following receipt of an I/O Halt signal. Timing pulses TP4 and TP5 are supplied to terminals 39 and 40 of the data break interface connector 1J03 for use in input-output equipment as well as for use in the processor.

The timing pulses which control cyclic memory functions are generated by transistor gating circuits which combine the conditions of various flip-flops in the 4-bit counter directly and through delay lines. Since the TP pulses which produce operations in the processor and the memory control signals are derived from the same timing source (the 1-megacycle crystal clock), the processor and the core memory are synchronized. During each computer cycle, core memory is in the read status during time states T2 and T3 due to the presence of the Memory Read signal derived from the binary 1 state of flip-flop TG<sub>2</sub> and is in the write state during time states T5 and T6 due to generation of the Memory Write signal derived from the binary 1 status of flip-flop TG<sub>0</sub>. The Memory Strobe pulse, which allows the sense amplifiers to sample information induced on the sense windings during the read operation, is a DEC standard negative pulse produced by a circuit of the 1607 Pulse Amplifier module of 1A01. Operation of this pulse amplifier is initiated 600 nanoseconds after the start of the Memory Read signal, except under the conditions specified by the signal supplied to the 4-input negative NOR diode gate of the 4115 module at location 1C18. This gate inhibits generation of the Memory Strobe pulse during the program count state of a JMP or JMS instruction, during the execute 1 state of a DCA instruction, during the execute 2 state of a JMS instruction, or during a data break in which the direction of data transfer is into the PDP-5. To assure that data bits containing zeros are inhibited during writing, the Memory Inhibit signal is generated beginning 200 nanoseconds after the end of the Memory Read signal and ending with expiration of the Memory Write signal. The Memory Inhibit signal is generated as a function of the binary 1 state of flip-flop TG<sub>1</sub> by

the 2-transistor NOR circuit composed of inverter ST of the module at location 1C19 and inverter UVW of the module at location 1A01. The 1311 Delay Line module at location 1C20, whose output line is normally held at - 3 volts by clamped load resistor F of the module at 1D07, and the inverter ST inhibit generation of the Memory Inhibit signal during the first 200 nanoseconds of the 1 state of TG<sub>1</sub>. The inverter UVW assures turn off of the Memory Inhibit signal as soon as TG<sub>1</sub> reverts to the 0 state.

### OPERATOR CONSOLE (WD-D-5-0-10)

The operator console provides a means of manually controlling the operation of the computer, manually inserting data into flip-flop and core memory registers, and provides visual indication of the contents of the most important registers and control flip-flops. Wiring connections to the keys and switches on the operator console are shown on engineering drawing WD-D-5-0-10, and the logic signal level gating of the signals produced by the keys and switches is indicated on engineering drawing BS-D-5-0-5. Indicator lamps and drivers are shown on the appropriate replacement schematic drawings; connections to these drivers are indicated on cable lists CL-A-5-0-20 and 21, and the isolating resistors and connections between flip-flops or registers and the input to the indicator drivers are shown on the appropriate block schematic engineering drawings for the registers or control flip-flops.

#### Interlock and POWER Switches

One deck of the interlock switch is connected in parallel with the POWER switch so that if either of these switches is closed, a short circuit is provided between terminals 2 and 4 of the 832 Power Control. This short circuit supplies primary power to the coils of the time-delay relays which control the application of primary power to the power supplies. The POWER indicator is connected directly between ground and the -15 volt output of one of the power supplies and therefore lights to indicate the presence of secondary power.

A second deck of the interlock switch supplies either ground or -15 volts to the circuits of the keys and switches on the operator console. When this switch is in the locked position, ground potential is supplied to these circuits to disable them. When the switch is unlocked, -15 volts

enables the switch circuits. Therefore, in the locked position the interlock switch prevents power turn off by means of the POWER switch and disables all of the keys and switches on the operator console except the SWITCH REGISTER toggle switches.

### **Key Circuits**

When the computer is energized and the interlock switch is in the unlocked position, operating any of the keys or setting either the SINGLE STEP or SINGLE INST switch to the right position supplies -15 volts to an appropriate terminal of connector 1H04. Negative 15-volt signals supplied to this connector are combined in transistor and diode gating circuits shown in the lower left portion of engineering drawing 5. These diode-transistor gating circuits produce the Key Manual signal (which initiates operation of the special pulse generator) and produce other conditioning signal levels (which enable appropriate gates which are triggered by SP pulses during manual operations).

#### Indicator Circuits

Indicators on the operator console are 28-volt incandescent lamps driven by 4903 Light Bracket Assemblies or 4904 Short Light Bracket Assemblies. These assemblies contain a number of series circuits consisting of a transistor switch connected between an indicator and ground potential. One side of each of the indicators is connected in common to -15 vdc. Ground potential is connected in common to the emitter of each transistor switch through parallel-connected diodes which provide the appropriate emitter-base junction bias. Each transistor switch is turned on by a negative signal level applied to the base through a 3000-ohm resistor connected to the output of a flip-flop. When the output of a flip-flop is at ground potential, the transistor switch is cut off, and the circuit to the indicator lamp is incomplete. When the output of the flip-flop is at -3 volts, the transistor switch is closed to energize the indicator with approximately 14 volts.

### SWITCH REGISTER Toggle Switch Circuits

The 12 toggle switches which comprise the switch register (SR) supply enabling or disabling signal levels to the level input of positive capacitor-diode gates of the input mixer to allow the condition of the switches to be sensed automatically by the OSR instruction. A switch set

to the up position corresponds to a binary 1, and supplies a ground-potential enabling signal level to a capacitor-diode gate of the appropriate bit of the input mixer through a 1k resistor and a terminal of connector 1H04. A switch in the down position corresponds to a binary 0, and supplies a -15 volt signal to disable an input mixer capacitor-diode gate through the same path. Connections to the input mixer from the SR are indicated on engineering drawing 14.

## RUN AND I/O HALT CONTROL (5)

Control of the circuits which produce the timing signals of the PDP-5, and hence which control automatic operation of the computer, is exercised by the run and I/O-hlt flip-flops. These flip-flops and their associated input gating circuits are shown on the right side of engineering drawing 5. The run flip-flop enables the timing circuits to generate timing signals when in the 1 state. The 1 output from this flip-flop is also supplied to terminal 42 of the data break interface connector 1J03 (via a bus driver circuit shown on engineering drawing 31). The I/O-hlt flip-flop provides a means of setting and clearing the run flip-flop by means of signals supplied by an I/O device.

The run flip-flop is cleared by a positive pulse that grounds terminal U of the 4215 module at location 1D01 under one of the following conditions:

- a. During the power turn off and turn on sequence by the Power Clear pulses.

- b. By an SPO pulse following operation of either the START, LOAD ADDRESS, EXAMINE, DEPOSIT, or CONTINUE key.

- c. By a TP6 pulse to conclude operations when the STOP key is pressed or to conclude an operation when the SINGLE STEP or SINGLE INST switches are in the on (right) position.

- d. By a TP5 pulse during an operate 2 instruction in which bit 10 is a 1 to provide a programmed halt.

- e. By the positive transistion of the signal at terminal 1D01N when the I/O-hlt flip-flop changes from the 0 to the 1 state.

The run flip-flop is set by a positive pulse that grounds terminal T under one of the following conditions: